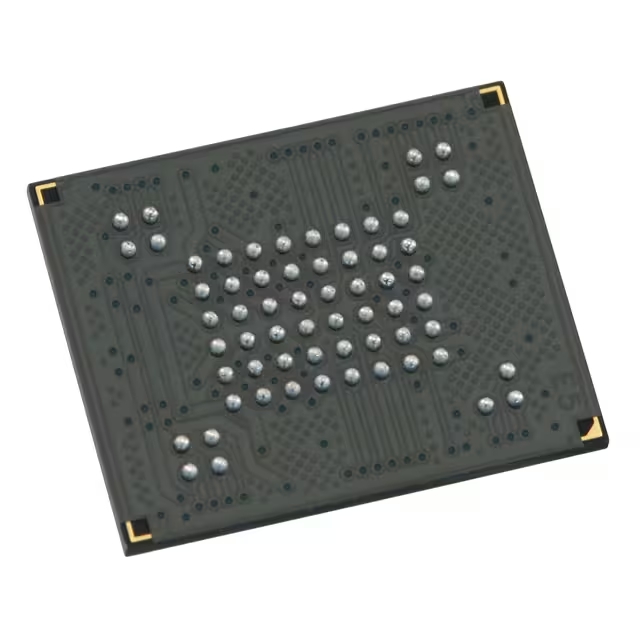

MT29F2G08ABAEAH4:E データシート、価格、PDF

- メモリタイプ: 不揮発性

- メモリフォーマット: フラッシュ

- テクノロジー: フラッシュ - NAND

- パッケージ: 63-VFBGA

HK$250.00以上のご注文で送料無料

迅速な対応、迅速な見積もり

すぐに発送、アフターサービスも安心

オリジナルチャネル、本物の製品の保証

Mt29f2g08abaeah4:E

信頼性の高いNANDフラッシュストレージをお探しなら、MicronのMT29F2G08ABAEAH4:Eが最適です。この2Gb(256MB)SLC NANDチップは優れた耐久性を備え、頻繁な書き込み・消去サイクルに最適です。2.7V~3.6Vでスムーズに動作し、-40℃~+85℃の温度範囲に対応し、コンパクトな63ボールVFBGAパッケージで提供されます。パラレルインターフェースはONFI 1.0規格に準拠しており、多くのコントローラとの互換性を確保しています。組み込みシステム、産業用制御、民生用電子機器、データロギングアプリケーションに最適です。詳細な統合ガイドラインについては、Micronのデータシートをご確認いただくか、正規販売代理店にお問い合わせください。

Mt29f2g08abaeah4:E ピン配置

| ピン名 | タイプ | 機能説明 |

|---|---|---|

| エール | 入力 | アドレスラッチ有効; 入力アドレスを高レベルでラッチ |

| CE# | 入力 | チップイネーブル信号;アクティブロー |

| クレ | 入力 | コマンドラッチ有効; コマンド入力を高レベルでラッチします |

| RE# | 入力 | 読み取りイネーブル信号。アクティブロー、チップからデータを読み取るために使用 |

| WE# | 入力 | 書き込みイネーブル信号。アクティブロー、チップにデータを書き込むために使用 |

| WP# | 入力 | 書き込み保護ピン。ローの時は書き込みまたは消去が無効になります。 |

| R/B# | 出力 | 準備完了/ビジー状態ピン。Low はビジー状態、High は準備完了状態を示します。 |

| 入出力[7:0] | 双方向 | コマンド、アドレス、およびデータの送信に使用されるデータ入力/出力ピン |

| VCC | 力 | チップ用電源(2.7~3.6 V) |

| VSS | 力 | チップのグランドピン |

| ノースカロライナ州 | 接続なし | ピンは内部で接続されていません。フローティングのままにするか、グランドに接続することができます。 |

| DNU | 予約済み | ピンは使用しないでください。浮かせたままにしてください。 |

MT29F2G08ABAEAH4:E NANDフラッシュチップを配線する際は、いくつか注意すべき点があります。まず、VCCを安定した2.7~3.6V電源に接続し、0.1µFのセラミックコンデンサを近くに配置して電源をクリーンに保ちます。ノイズを低減するため、グランドラインは短くしてください。ALE、CLE、CE#、WE#、RE#などの信号ピンは、干渉を最小限に抑えるため、配線を短くし、インピーダンスを整合させてください。WP#やR/B#などのピンは、VCCにプルアップ抵抗(10kΩ)が必要です。NCピンは信号や電圧に接続しないでください。また、チップの損傷を防ぐため、DNUピンは常にフローティングにしてください。最後に、電源投入後は必ずRESETコマンド(0xFF)から開始してください。

Mt29f2g08abaeah4:E 同等のNANDフラッシュ

| パラメータ | MT29F2G08ABAEAH4:E (オリジナル) | MT29F2G08ABAGAH4-IT:G | K9F2G08U0C-SCB0 | TC58NVG2S0HTAI0 | W29N02GVSI |

|---|---|---|---|---|---|

| メーカー | ミクロン | ミクロン | サムスン | 東芝 | ウィンボンド |

| 容量 | 2GB(256MB) | 2GB | 2GB | 2GB | 2GB |

| インターフェースタイプ | パラレルNAND | パラレルNAND | パラレルNAND | パラレルNAND | パラレルNAND |

| パッケージタイプ | 63ボールVFBGA | 63ボールVFBGA | 63ボールVFBGA | 63ボールVFBGA | 63ボールVFBGA |

| ページサイズ | 2048+64バイト | 2048+64バイト | 2048+64バイト | 2048+64バイト | 2048+64バイト |

| ブロックサイズ | 128K+4Kバイト(64ページ) | 128K+4Kバイト | 128K+4Kバイト | 128K+4Kバイト | 128K+4Kバイト |

| 動作電圧 | 2.7~3.6V | 2.7~3.6V | 2.7~3.6V | 2.7~3.6V | 2.7~3.6V |

| 動作温度 | -40℃~+85℃ | -40℃~+85℃ | -40℃~+85℃ | -40℃~+85℃ | -40℃~+85℃ |

| ONFI互換性 | オンフィ 1.0 | オンフィ 1.0 | オンフィ 1.0 | オンフィ 1.0 | オンフィ 1.0 |

| 持久力(P/Eサイクル) | 100,000 | 100,000 | 100,000 | 100,000 | 100,000 |

| データ保持 | 10年 | 10年 | 10年 | 10年 | 10年 |

NANDフラッシュチップを別のモデルに交換する場合は、以下の点に注意してください。まず、新しいチップのパッケージが元のチップと一致していることを確認してください。一致していないと、PCBを再設計することになります。パッケージが同一の場合でも、ピン配置を慎重に再確認してください。ブランドによって異なる場合があります。互換性を保つには、電圧範囲、ページサイズ、ブロックサイズなどの電気仕様を一致させてください。チップがONFI規格に対応していれば理想的ですが、コントローラーが交換品に対応していることを確認してください。最後に、特定の温度条件に適したチップを選択してください。最終決定を下す前に、必ずメーカーのデータシートを参照してください。

Mt29f2g08abaeah4:E インターフェース回路

NANDフラッシュチップの配線手順を簡単に説明します。8ビットデータバス(I/O[7:0])をコントローラに直接接続してデータ交換を行います。次に、いくつかの重要な制御信号があります。チップをアクティブ化するCE#、データの読み書きを行うRE#とWE#、そしてアドレスとコマンド情報をラッチするALEとCLEです。WP#は10kΩの抵抗を介して3.3Vにプルアップすることを忘れないでください。これにより、誤書き込みを防止できます。また、R/B#も同様にプルアップすることで、コントローラがチップがビジー状態かレディ状態かを把握できるようになります。電源に関しては、VCCを安定した3.3V電源に接続し、VSSを直接グランドに接続します。

Mt29f2g08abaeah4:E Spi NANDの例

MT29F2G08ABAEAH4:E NANDフラッシュチップのご使用をご検討中の場合は、パラレルインターフェース用に設計されていることにご注意ください。つまり、複数のデータライン(通常8ビット)と、CE#、WE#、RE#、ALE、CLEなどの専用制御信号を使用して通信します。この設計により、高速データ転送とリアルタイム性能が実現され、組み込みシステム、産業用制御システム、データロガーなどに最適です。

しかし、ここで問題があります。SPIは、より少ないピン(通常はCS、MOSI、MISO、SCLKの4つ)を使って1ビットずつデータを転送する、よりシンプルなシリアルインターフェースです。PCBのスペースやGPIOピンが限られている場合、SPIチップは最適です。

レイアウトの簡素化やリソースの節約のためにSPIを必要とする設計の場合は、MT29F1G01ABAFDWBやMT29F2G01ABAFDWBなどの専用SPI NANDチップのご使用をお勧めします。これらのチップにはSPIコントローラが内蔵されており、コンパクトな設計、すっきりとした配線、そして低消費電力を簡単に実現できます。

Mt29f2g08abaeah4:E タイミング図

MT29F2G08ABAEAH4:E NANDフラッシュのタイミング図には、リセット、ステータス読み出し、ページ読み出し、ページプログラム、ブロック消去の各動作が含まれます。以下では、特に以下の詳細なタイミングについて解説します。 読み取りステータス 手術。

MT29F2G08ABAEAH4:E NANDフラッシュが「ステータス読み出し」操作を実行する仕組みを詳しく説明しましょう。まず、ステータスコマンド(70h)をチップに送信します。これを行うには、CLEラインをハイレベル(チップにコマンド送信を通知)にし、CE#ラインをローレベルにしてデバイスを選択します。次に、WE#ラインをローレベルにして書き込みをトリガーします。これにより、データバス(I/O[7:0])を介してコマンドがチップにラッチされます。

このコマンドを正しく送信した後(tCLS、tCS、tWPなどのタイミングパラメータを注意深く監視してください)、CLEを下げてコマンドフェーズの終了を知らせます。これでチップは応答準備完了です。

次に、RE#をローレベルにします。これにより、チップは内部ステータスをデータラインに送信するようになります。短い遅延(tREA)の後、ステータスがデータバスに表示され、コントローラが読み取れる状態になります。ステータスを取得したら、RE#とCE#をハイレベルに戻して完了です。チップはスタンバイ状態に戻り、次のコマンドを待ちます。

Mt29f2g08abaeah4:E Linux ドライバー

MT29F2G08ABAEAH4:EのようなNANDフラッシュチップをLinuxで使用する場合、通常はMTD(Memory Technology Device)サブシステムを介して実行されるため、生のフラッシュメモリの操作が容易になります。Linuxでは、NANDドライバを3つの主要なレイヤーに分割しています。一般的なコマンド(読み取り、書き込み、消去など)を扱うMTDレイヤー、特定のNANDコマンドとタイミングを管理するNANDドライバレイヤー、そしてGPIO信号とデータラインを扱うハードウェアコントローラレイヤーです。

Linuxは起動時に、まずResetコマンドやRead IDコマンドなどのコマンドを送信し、ページサイズやブロックサイズなどのパラメータをチェックすることでチップの種類を識別します。次に、読み取り/書き込みリクエストをNAND固有のコマンド(読み取りの場合は00h、ページプログラミングの場合は80hと10hなど)に変換して処理します。また、ドライバーはECC(エラー訂正)を管理してデータエラーを防ぎ、不良ブロックを追跡することで、システムの長期的な信頼性を維持します。

Mt29f2g08abaeah4:E ブートメモリ使用量

組み込みシステムを設計していて、MT29F2G08ABAEAH4:E NANDフラッシュをブートメモリとして使用する予定の場合、その動作は次のようになります。起動時に、プロセッサの内部ROMは専用コントローラを介してNANDと通信します。そして、NANDに保存されているブートローダ(U-Bootなど)を取得し、RAMにロードして実行します。

しかし、ここで重要な点があります。NANDフラッシュには、不良ブロックやビットエラーが発生する場合があります。この問題に対処するには、ブートプロセスにエラー訂正(ECC)と適切な不良ブロック管理が含まれていることを確認する必要があります。これにより、システムが常に確実に起動するようになります。

通常、NANDチップをパーティションに分割し、ブートローダー、オペレーティングシステムカーネル、ルートファイルシステムを別々に保存します。これにより、整理された構造が構築され、システムのスムーズな起動とデータの安全性が確保されます。

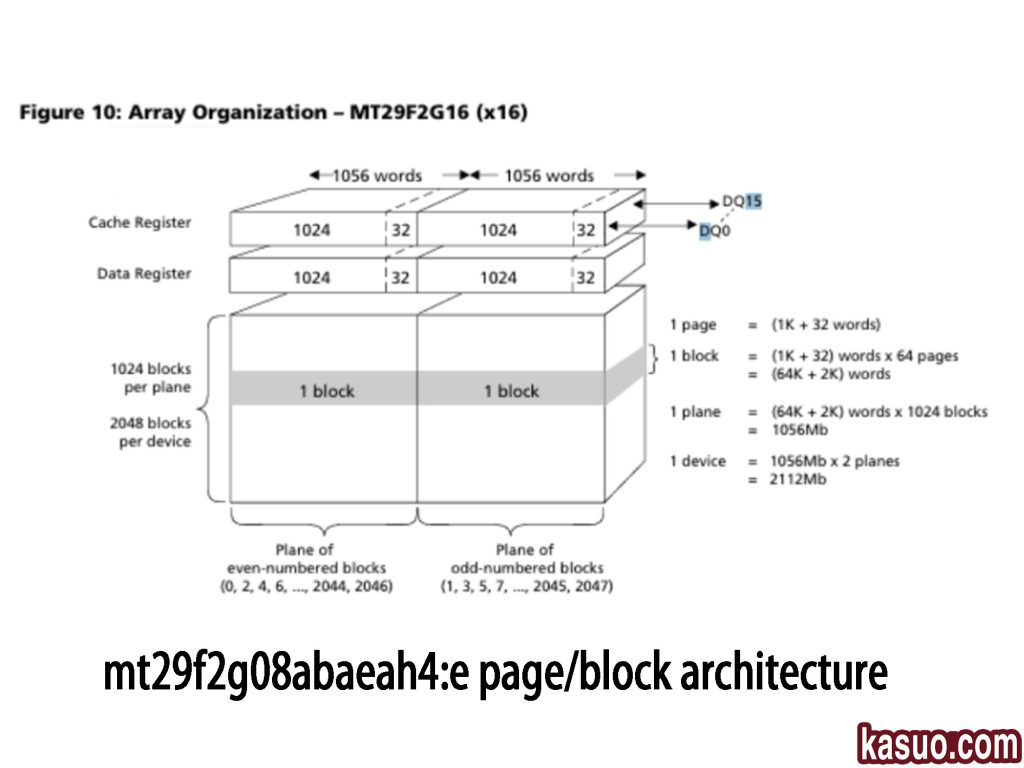

Mt29f2g08abaeah4:E ページ/ブロックアーキテクチャ

MT29F2G16 NANDフラッシュチップをお使いの方のために、そのストレージ構造を簡単にご説明します。各メモリページは1056ワードで構成されています。そのうち1024ワードは実際のデータ用で、残りの32ワードはOOB領域と呼ばれ、エラー訂正(ECC)や不良ブロックの管理などに使用されます。

これらのページはブロックにグループ化されており、各ブロックには64ページ、合計66Kワード(データ用64K、OOB用2K)が含まれます。さらに、ブロックは「プレーン」と呼ばれるより大きなセクションに分割され、各プレーンは1024ブロックで構成され、プレーンあたり約1056MBのストレージ容量となります。

チップ全体には2つのプレーン(1つは奇数ブロック、もう1つは偶数ブロックを処理)があり、合計2048ブロック、合計容量は2112MB、つまり約2GBです。このレイアウトを理解することで、データをより効率的に管理し、システムを整理することができます。