**Características**

JESD204B (subclase 1) Velocidad de canal de salida digital en serie codificada hasta 15 Gbps

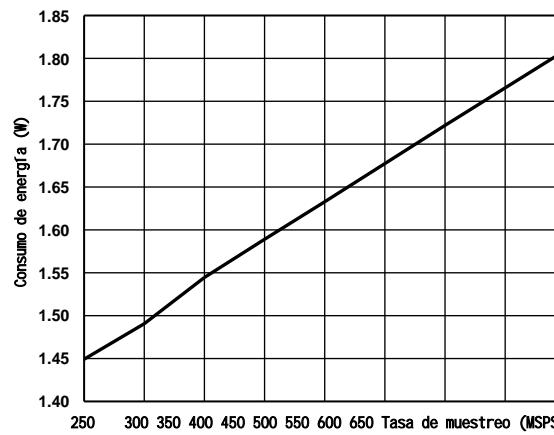

Potencia total de 1,66 W a 500 MSPS

415 mW por canal ADC

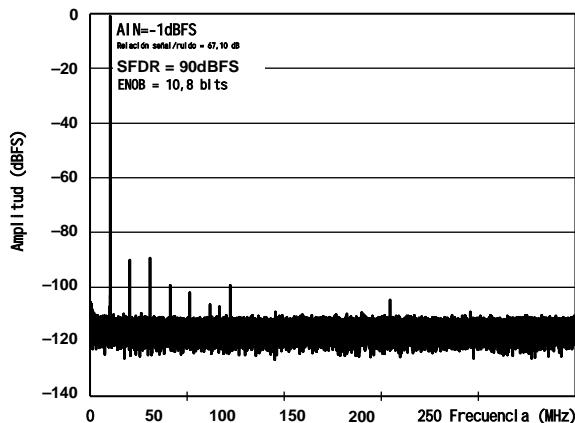

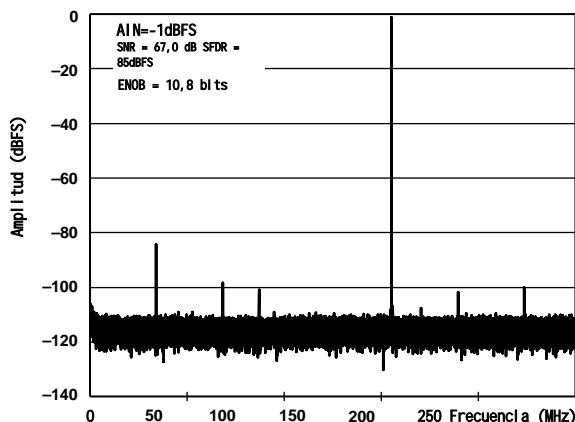

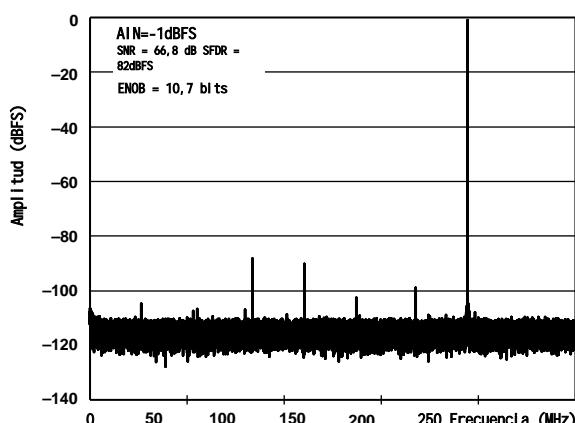

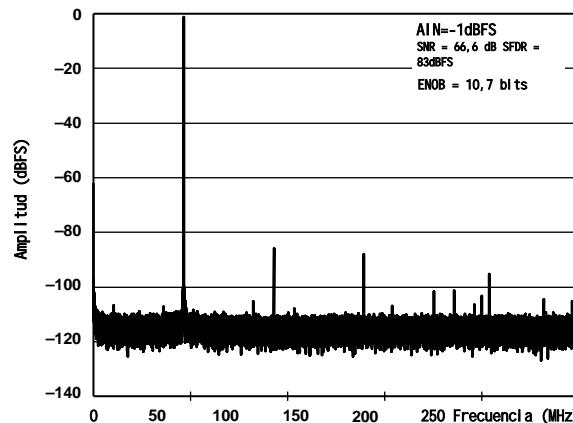

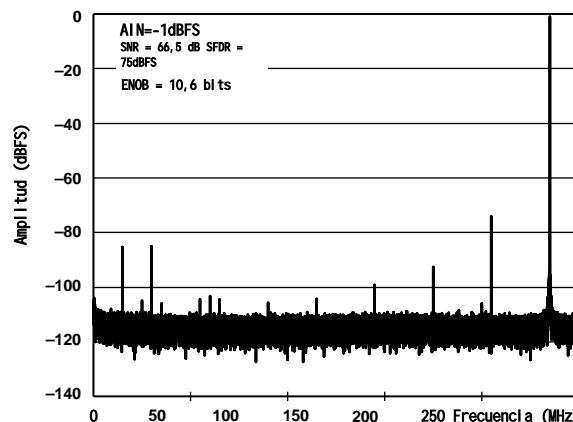

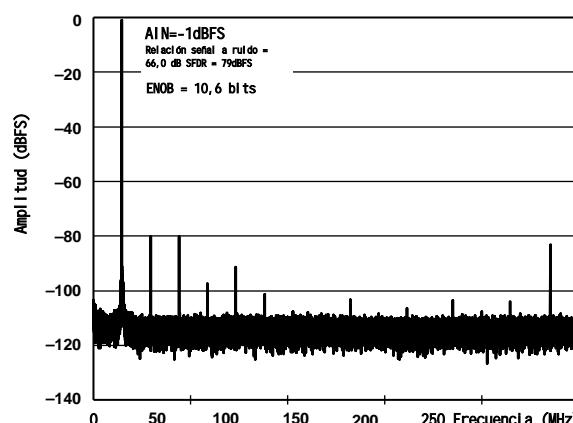

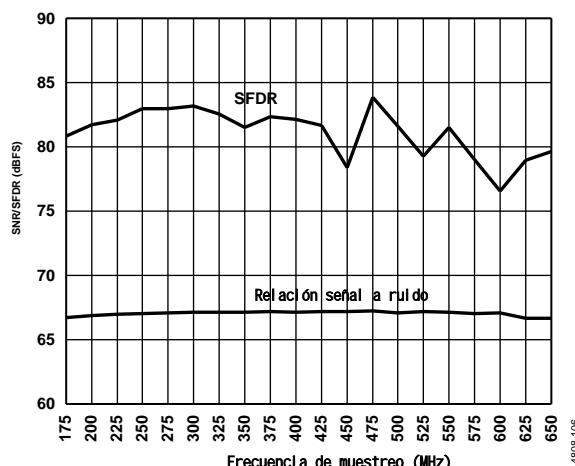

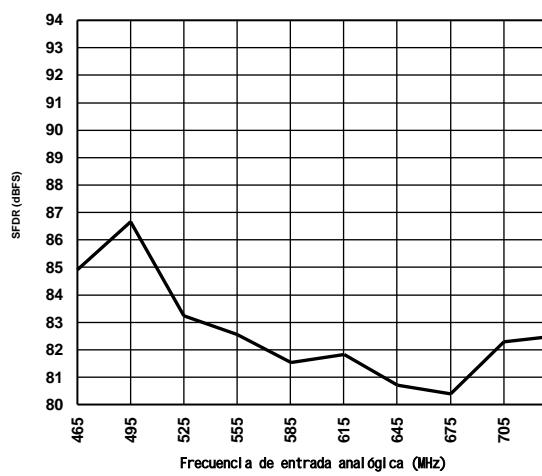

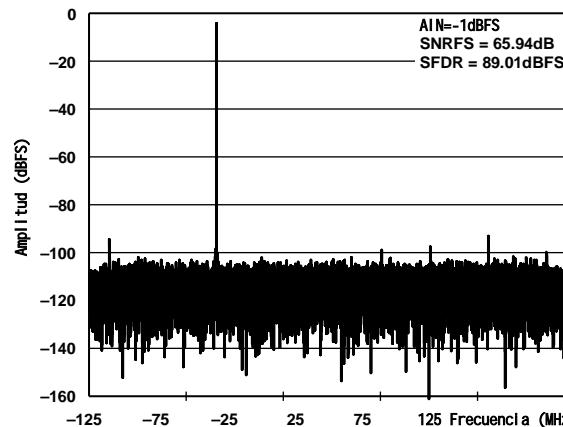

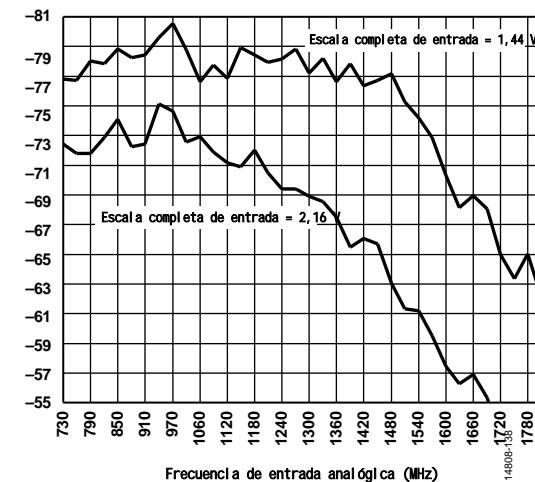

SFDR = 82 dBFS, 305 MHz (rango de entrada P-P de 1,80 V) SNR = 66,8 dBFS, 305 MHz (rango de entrada p-p de 1,80 V) Densidad de ruido = 151,5 dBFS/Hz (rango de entrada p-p de 1,80 V) Fuente de alimentación CC de 0,975 V, 1,8 V y 2,5 V Funciona sin código faltante

Búfer de entrada analógica de referencia de voltaje ADC interno

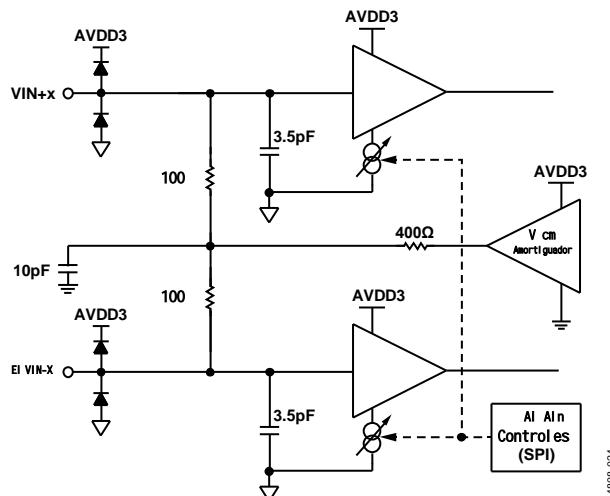

La fluctuación en el chip mejora la linealidad de señal al pequeña y el rango de entrada diferencial flexible

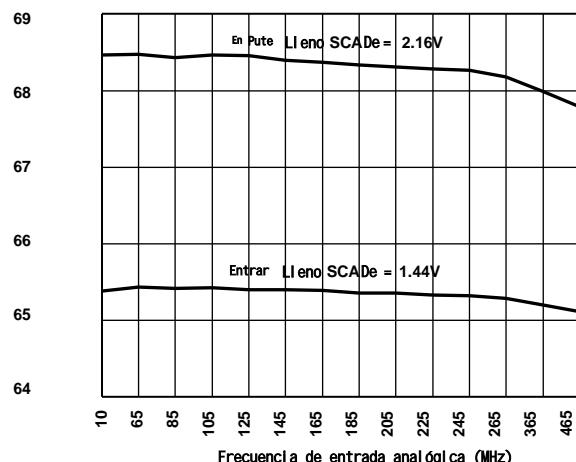

1.44 V p-p a 2,16 V p-p (nominal a 1,80 V p-p)

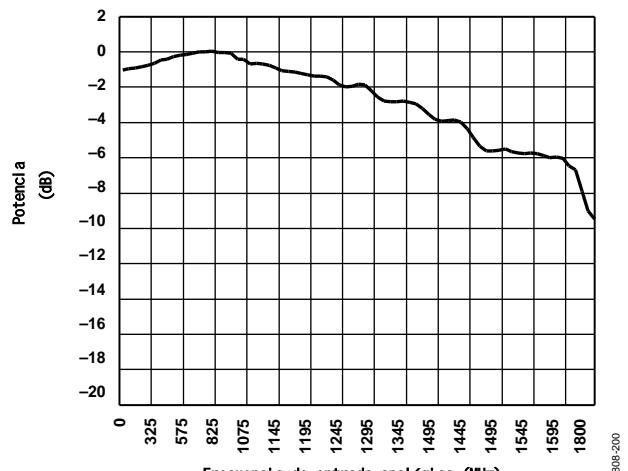

1.4 Entrada analógica de GHz Ancho de banda de potencia completo

Bits de detección de amplitud para implementación eficiente de AGC 4 procesadores digitales de banda ancha integrados

NCO de 48 bits, hasta 4 entradas de reloj diferentes con filtros de media banda en cascada

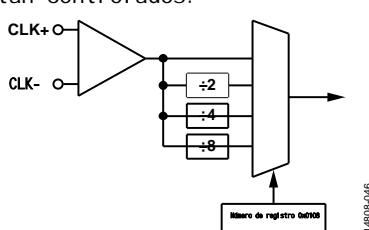

Reloj entero dividido por 1, 2, 4 u 8

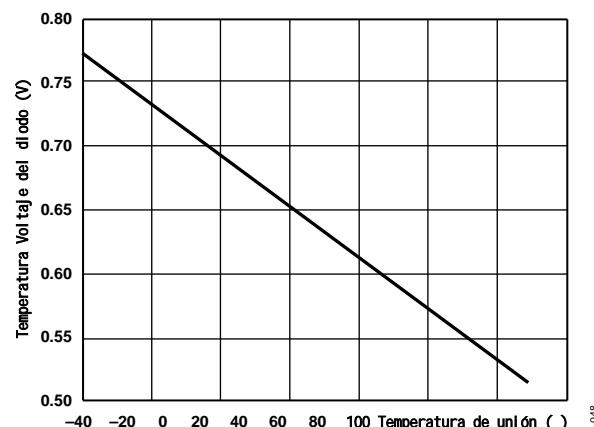

Diodo de temperatura en chip

Configuración flexible del canal JESD204B

**Aplicación**

**Comunicaciones**

Diversidad multibanda, multimodo receptor digital 3G/4G, W-CDMA, GSM, LTE, LTE-A

Instrumentación de receptor de satélite de banda ultra ancha de radio de software universal

**Radar**

**Inteligencia de señales (SIGINT)**

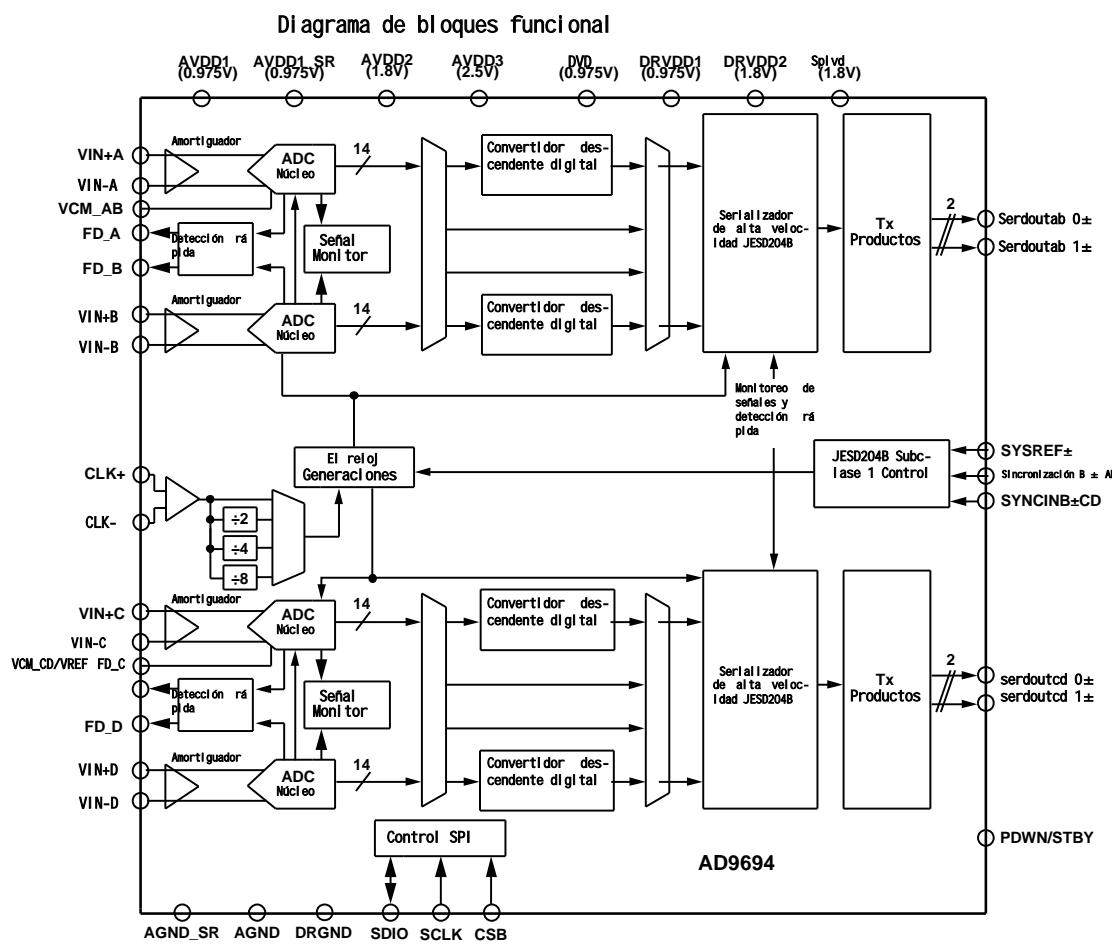

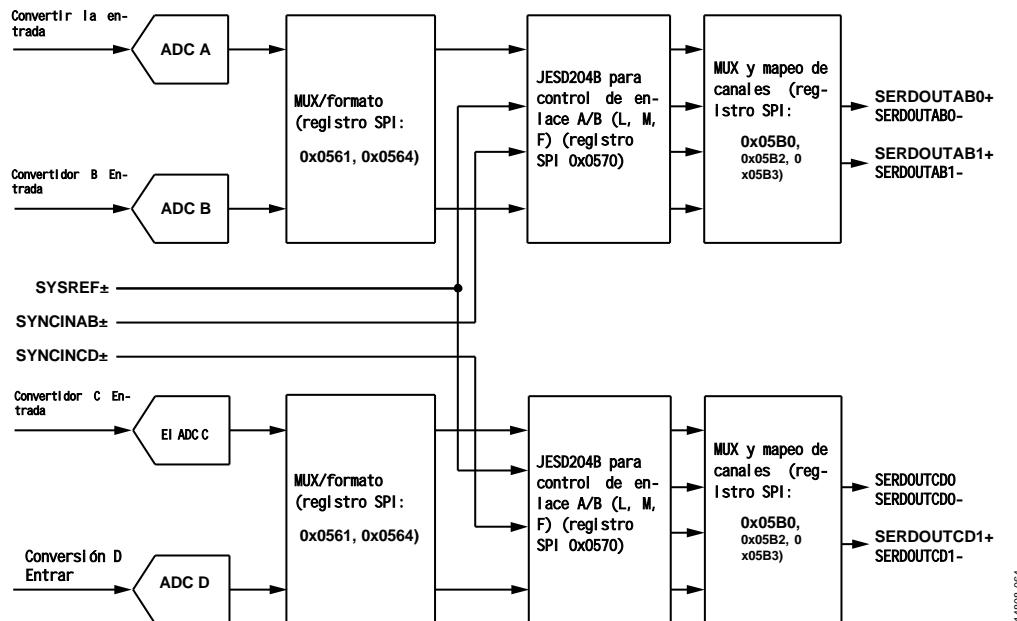

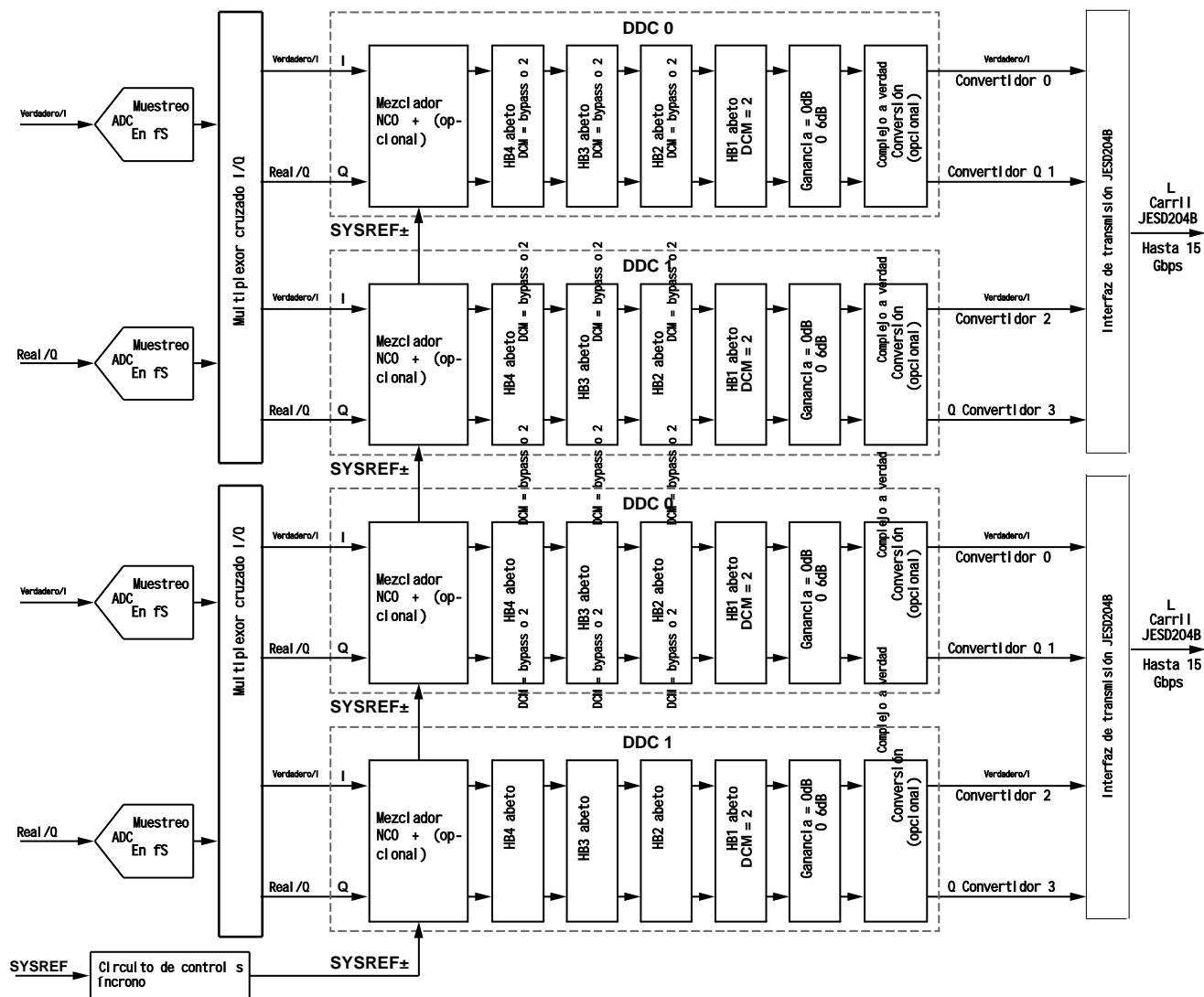

Figura 1.

14698-001

**Versión B**

**Retroalimentación de documentos**

La información proporcionada por Analog Devices se considera precisa y confiable. Sin embargo, Analog Devices no asume ninguna responsabilidad por su uso ni por cualquier infracción de patentes u otros derechos de terceros que pueda resultar de su uso. Las especificaciones están sujetas a cambios sin previo aviso. Ninguna patente o derecho de patente de Analog Devices otorga ninguna licencia, implícita o de otra manera. Las marcas comerciales y las marcas registradas son propiedad de sus respectivos dueños.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, EE. UU. Tel.: 781.329.4700 © 2016-2018 Analog Devices, Inc. Todos los derechos reservados.

Soporte técnico

World Wide Web. analog.com

## Catálogo

|                                                      |    |                                                             |    |

|------------------------------------------------------|----|-------------------------------------------------------------|----|

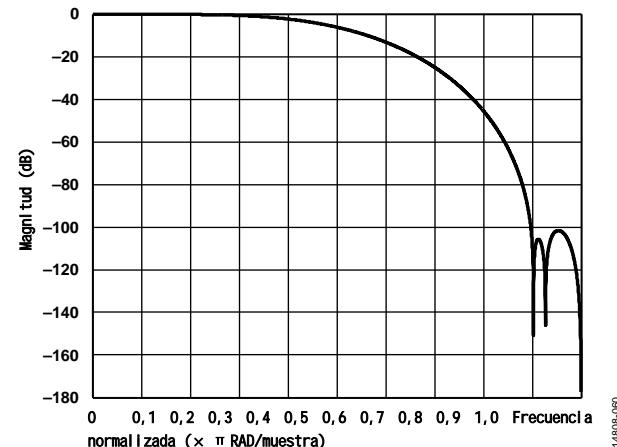

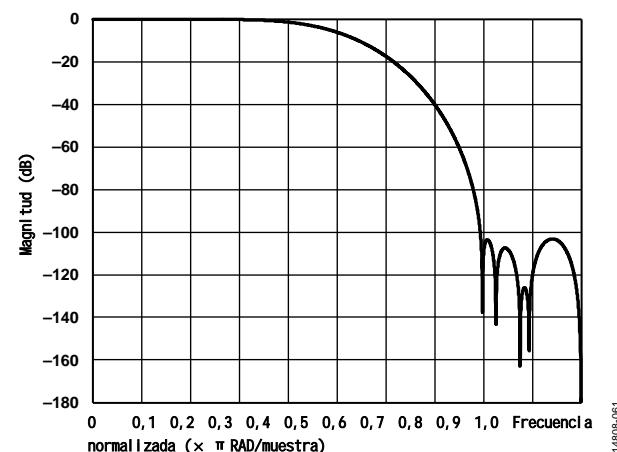

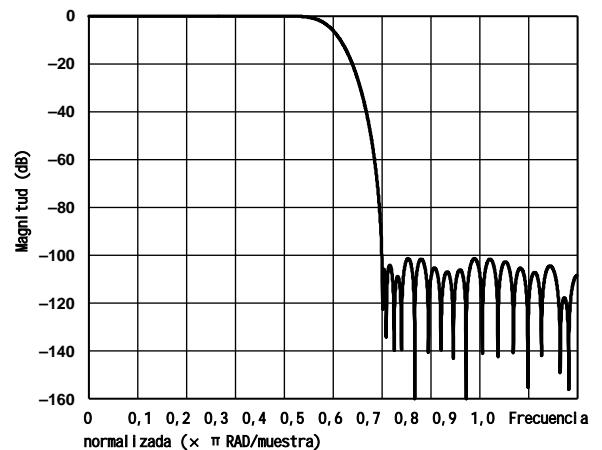

| Características                                      | 1  | Filtro de media banda                                       | 43 |

| Aplicación                                           | 1  | Etapa de ganancia DDC                                       | 44 |

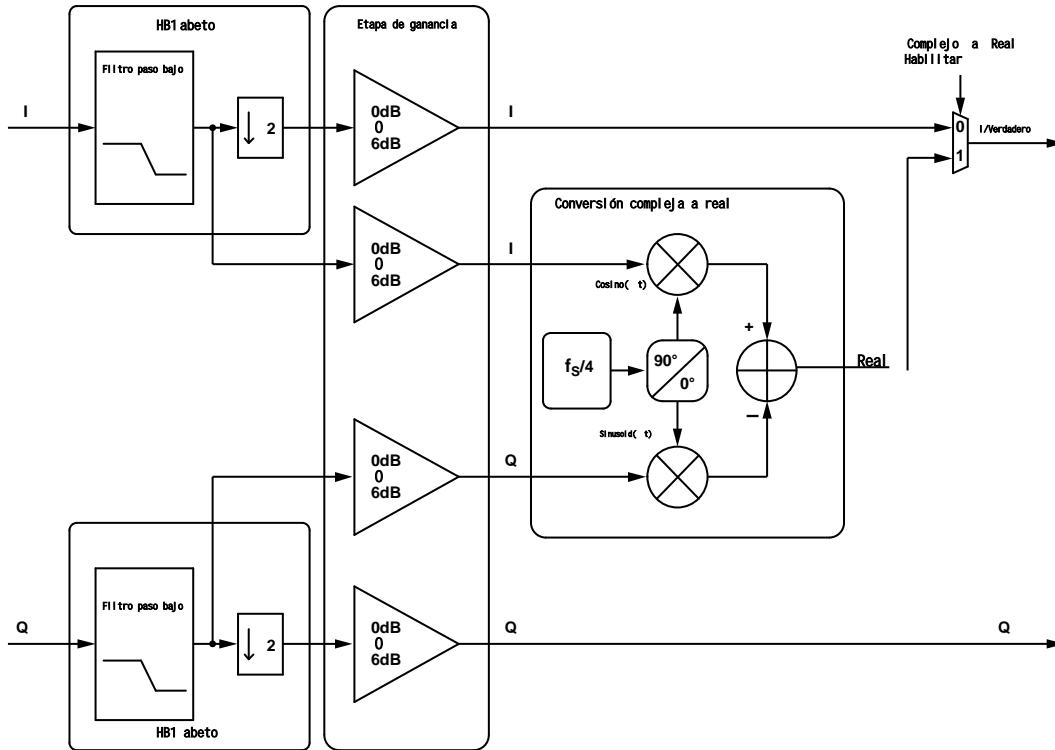

| Diagrama de bloques funcional                        | 1  | DDC Conversión de números complejos a reales                | 44 |

| Historial de revisiones                              | 3  | Configuración de ejemplo de DDC                             | 45 |

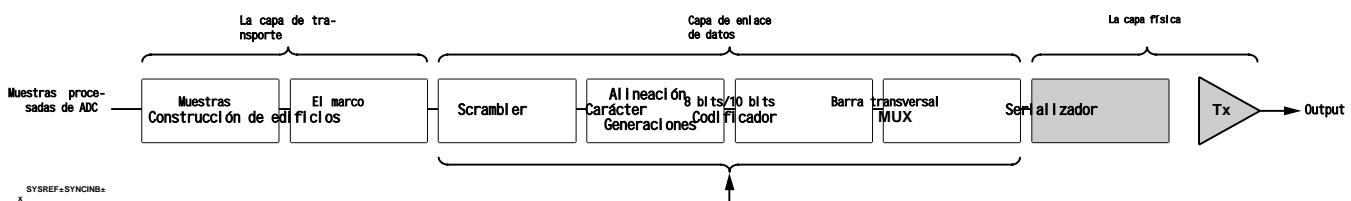

| Instrucciones generales                              | 4  | Salida digital                                              | 50 |

| Destacados del producto                              | 4  | Introducción a la interfaz JESD204B                         | 50 |

| Especificación                                       | 5  | Configuración de la interfaz digital AD9694                 | 50 |

| Especificaciones DC                                  | 5  | Descripción general de las funciones                        | 52 |

| Especificaciones AC                                  | 6  | Establecimiento de enlace JESD204B                          | 52 |

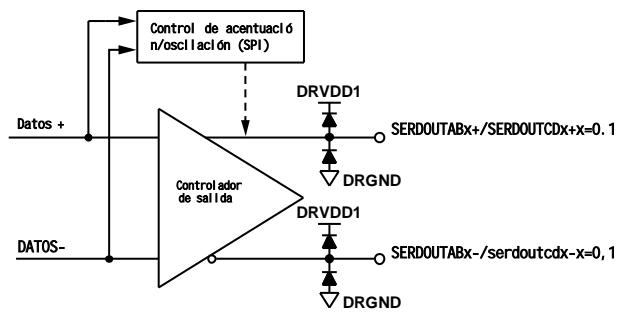

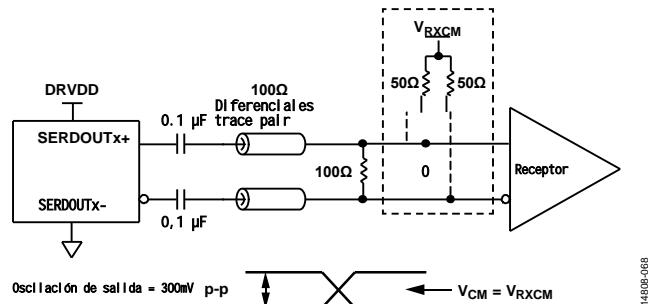

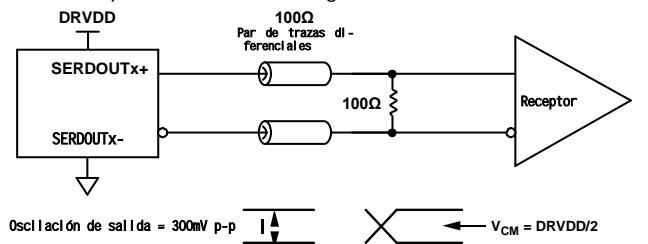

| Especificaciones digitales                           | 9  | Salida de la capa física (controlador)                      | 53 |

| ESPECIFICACIONES DEL                                 | 10 | Mapa del convertidor JESD204B Tx                            | 54 |

| Especificaciones de temporización                    | 11 | Configurar el enlace JESD204B                               | 56 |

| Calificación máxima absoluta                         | 12 | Retraso                                                     | 60 |

| Resistencia térmica                                  | 12 | Latencia total de extremo a extremo                         | 60 |

| ADVERTENCIA ESD                                      | 12 | Ejemplo de cálculo de retardo                               | 60 |

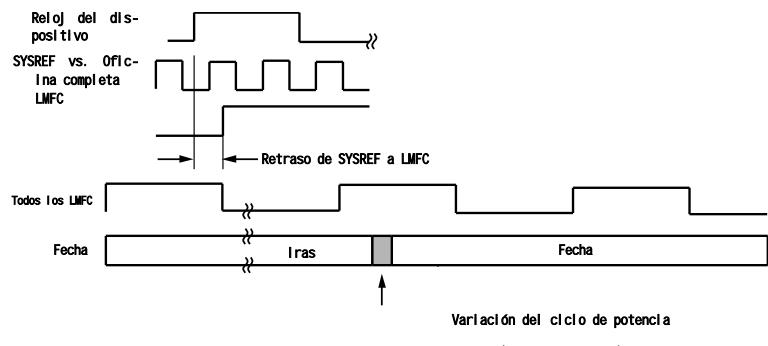

| Configuración de pines y descripción de la función   | 13 | Retraso de referencia LMFC                                  | 60 |

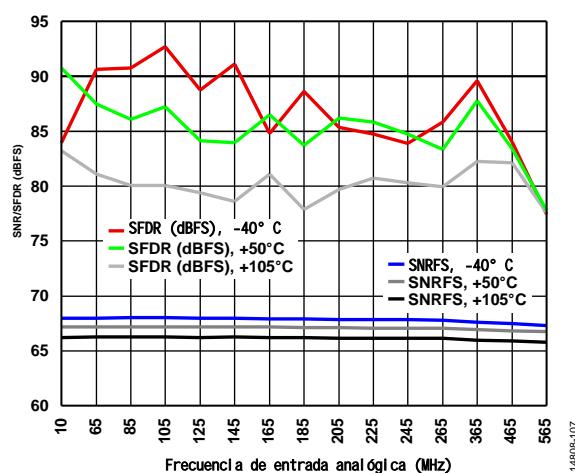

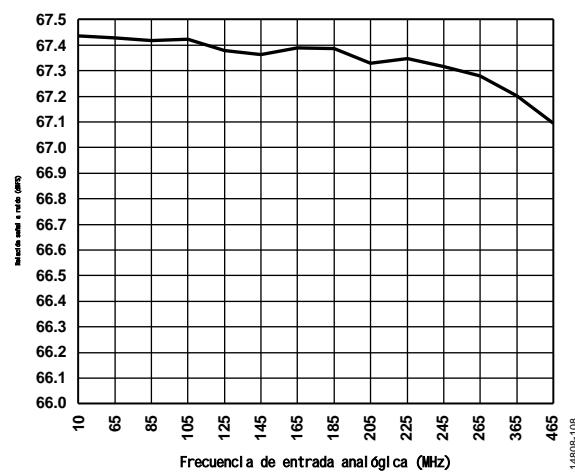

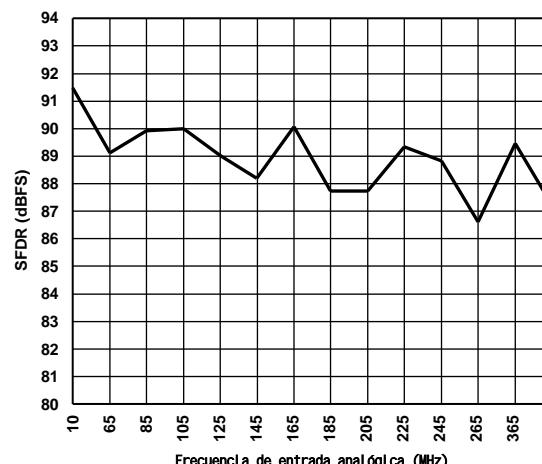

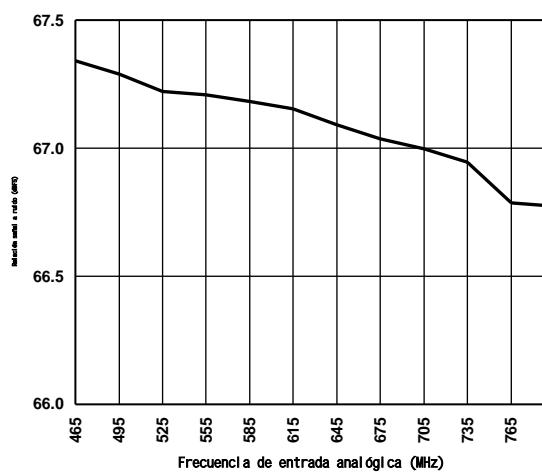

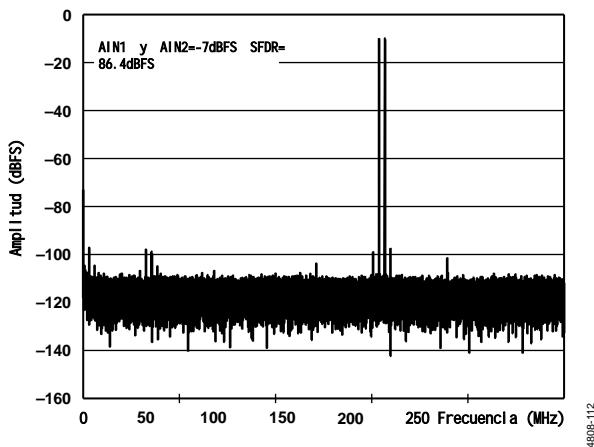

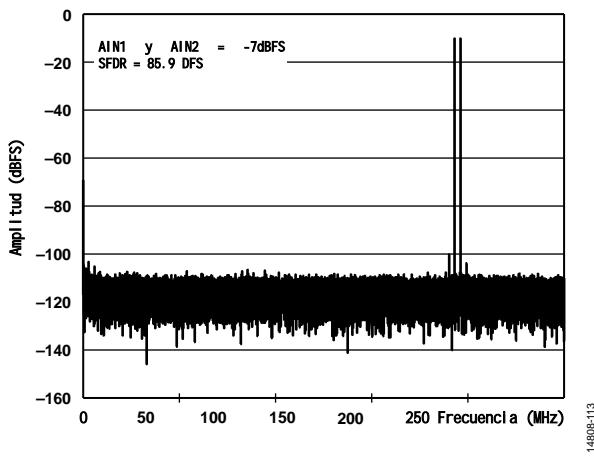

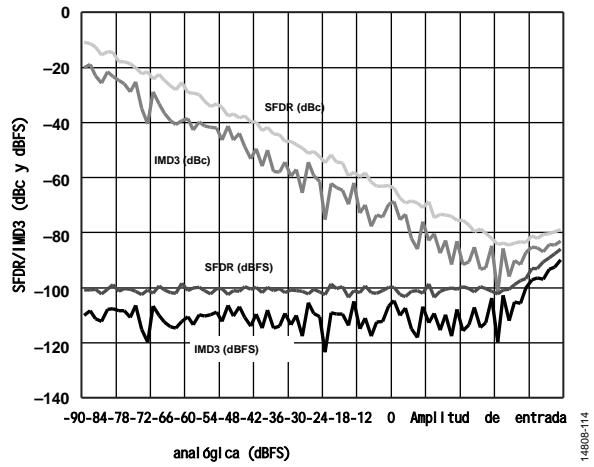

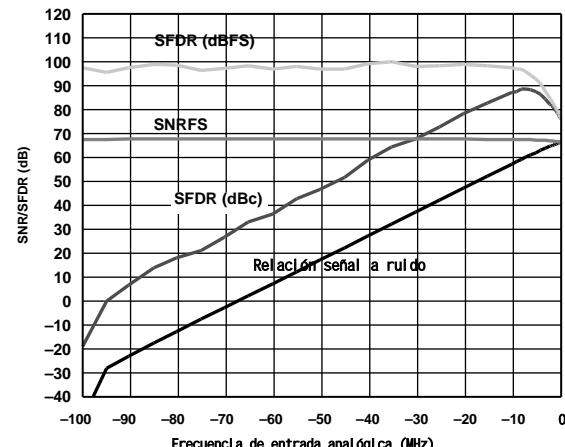

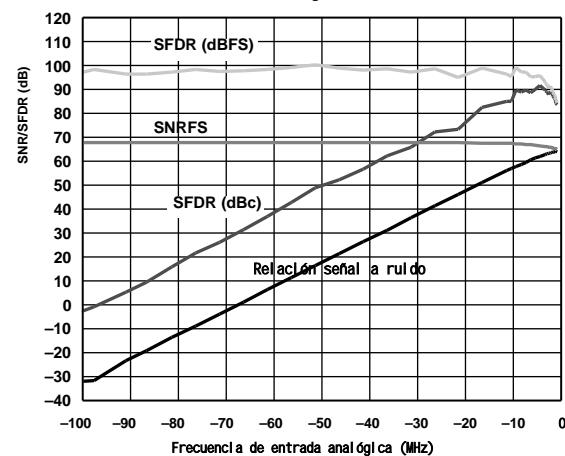

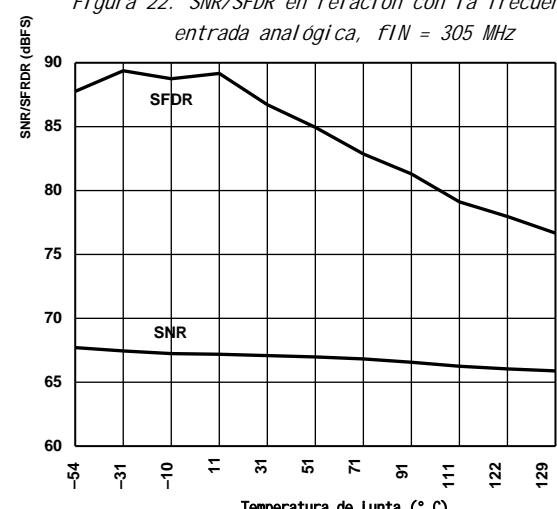

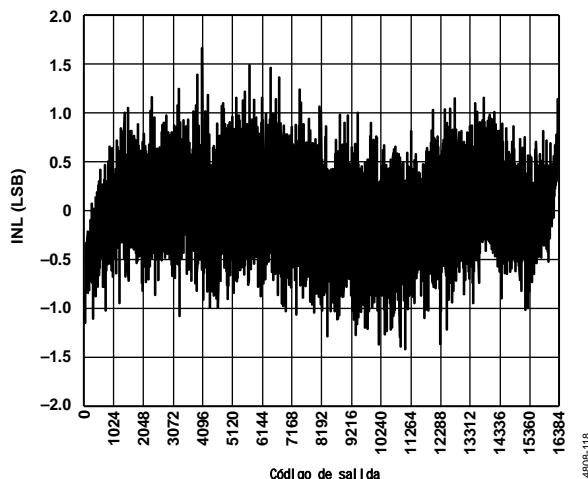

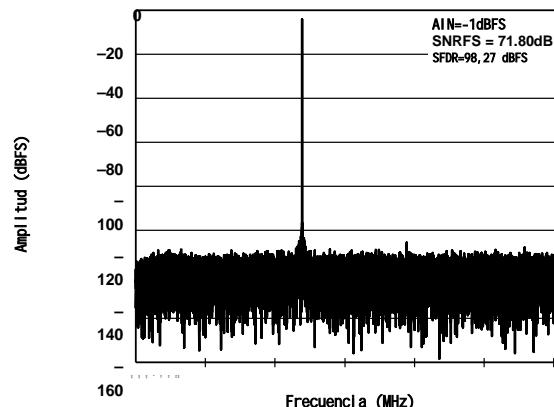

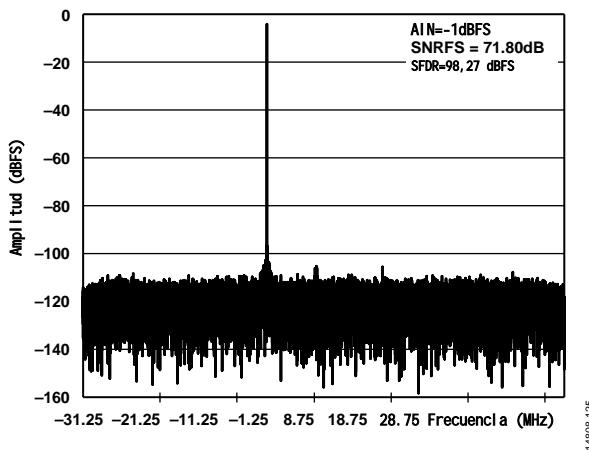

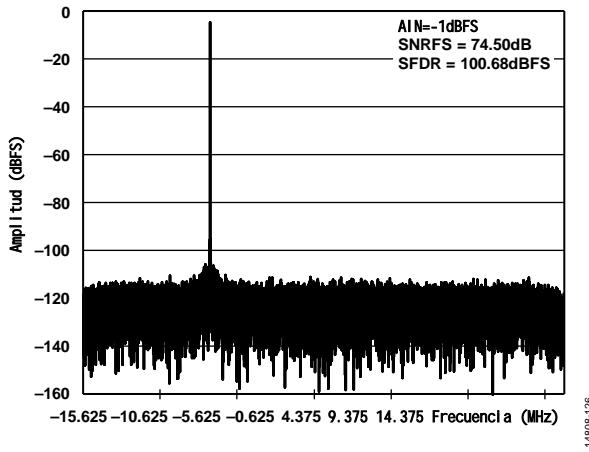

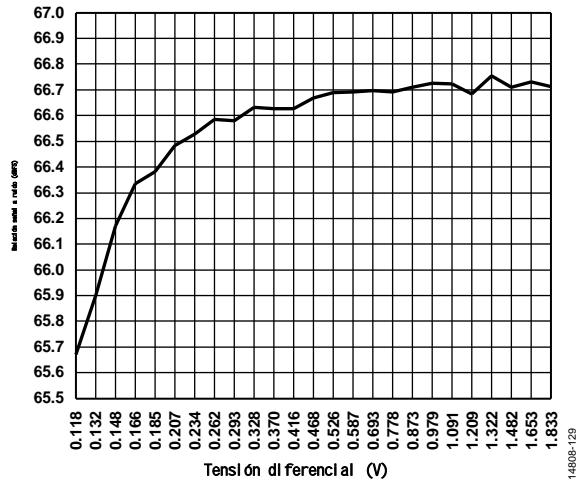

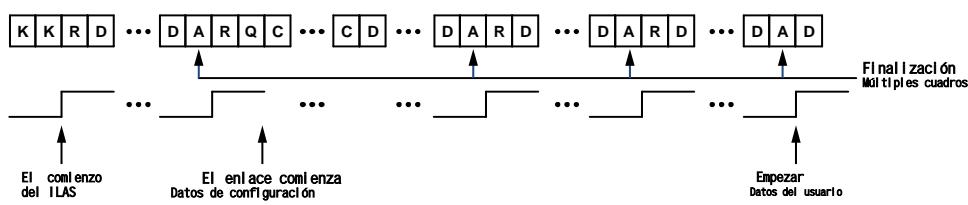

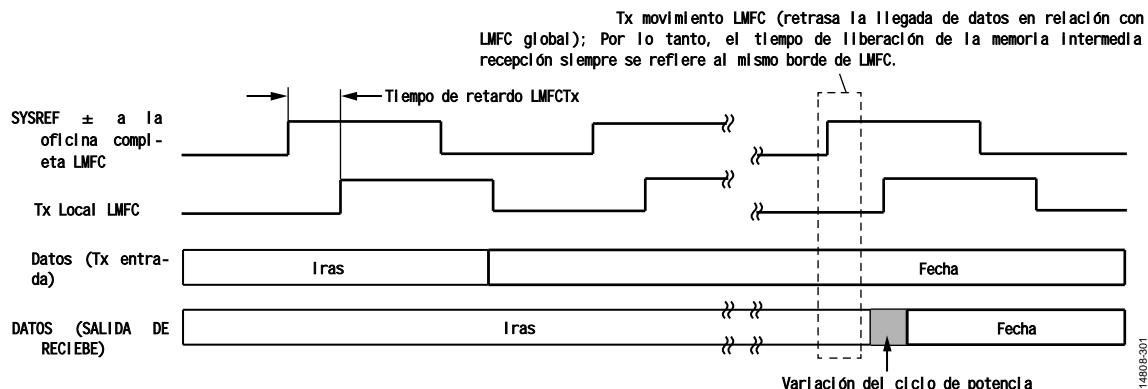

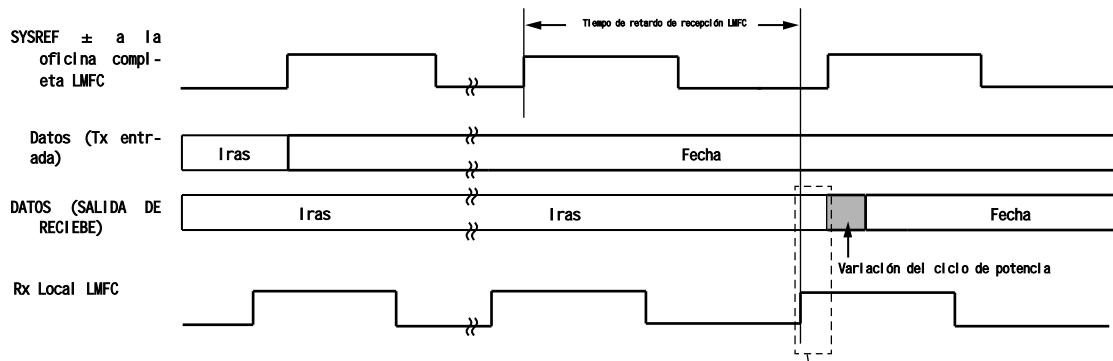

| Características de rendimiento típicas               | 15 | Deterministic retard                                        | 61 |

| Circuito equivalente                                 | 22 | Subclase 0 Operaciones                                      | 61 |

| Teoría de las operaciones                            | 24 | Subclase 1 Operaciones                                      | 61 |

| Arquitectura ADC                                     | 24 | Sincronización multichip                                    | 63 |

| Consideraciones de entrada analógica                 | 24 | Modo normal                                                 | 63 |

| Referencia de voltaje                                | 25 | Modo de marca de tiempo                                     | 63 |

| Calibración de polarización DC                       | 26 | SYSREF ± entrada                                            | 65 |

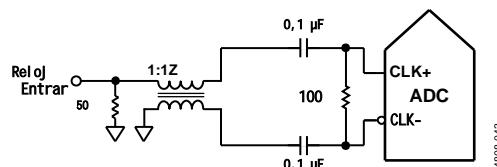

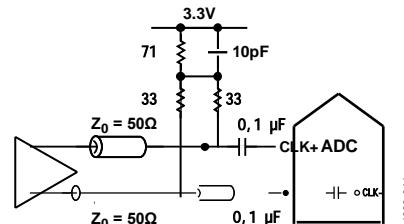

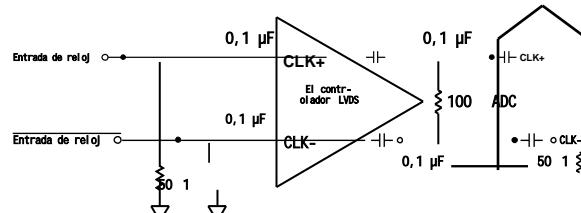

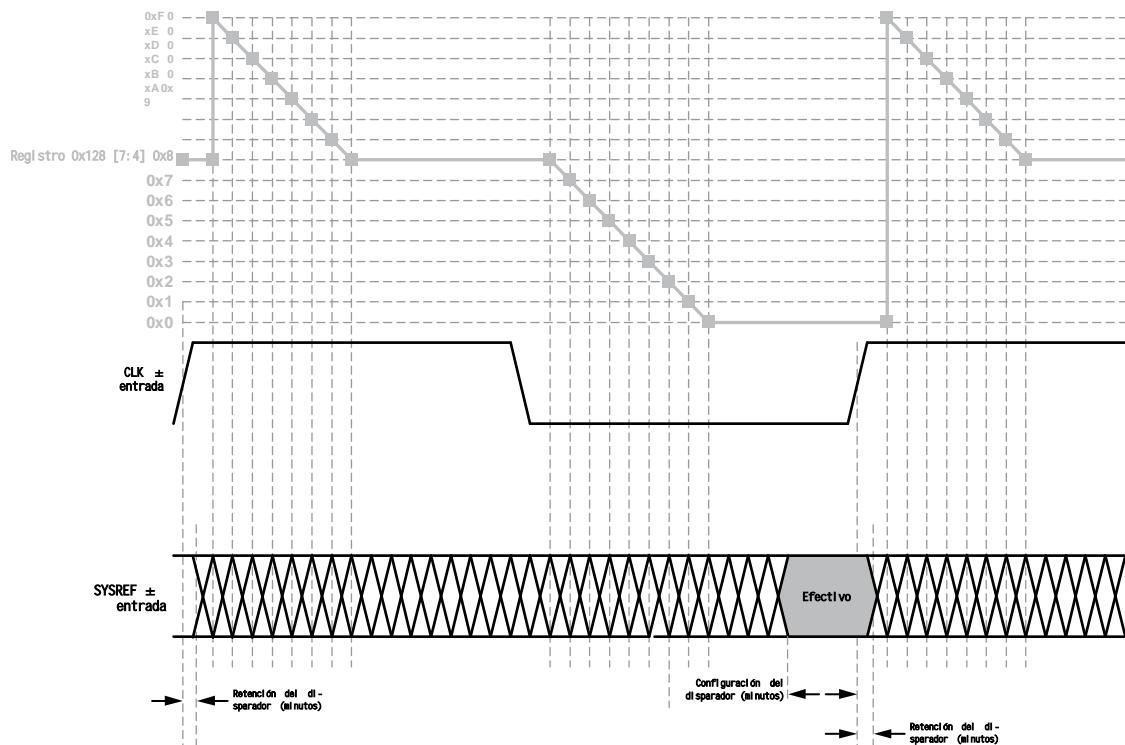

| Precauciones de entrada de reloj                     | 26 | SYSREF ± Configuración/mantenimiento del monitor de ventana | 66 |

| ADC fuera de rango y detección rápida                | 29 | Modo de prueba                                              | 68 |

| ADC fuera del rango                                  | 29 | Modo de prueba ADC                                          | 68 |

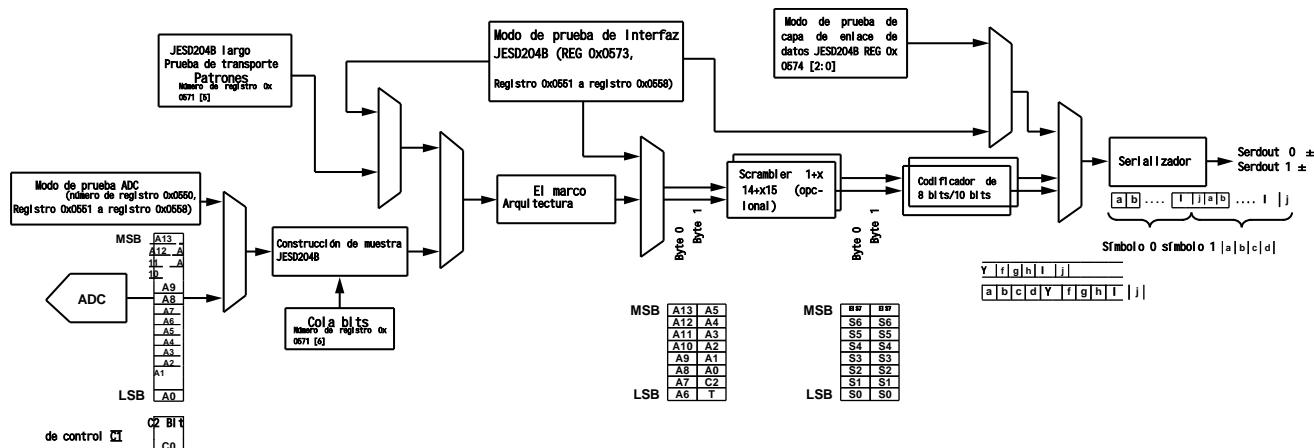

| Detección rápida de umbral (FD_A, FD_B, FD_C y FD_D) | 29 | Modo de prueba de bloque JESD204B                           | 69 |

| Monitor de señal                                     | 30 | Interfaz serie                                              | 71 |

| Movimiento en JESD204B                               | 30 | Configuración con SPI                                       | 71 |

| Convertidor descendente digital                      | 33 | Interfaz de hardware                                        | 71 |

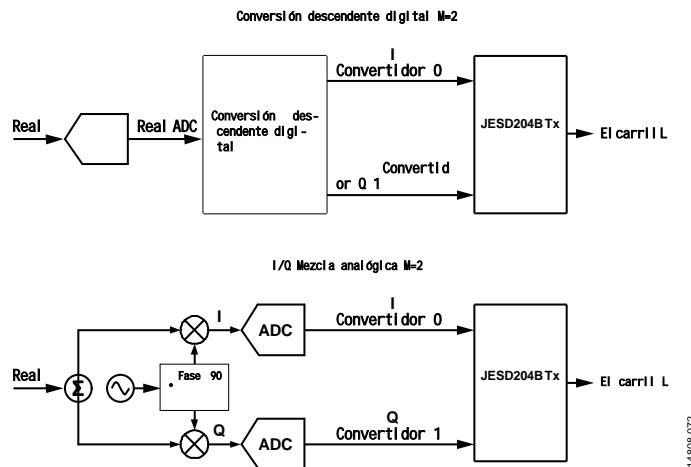

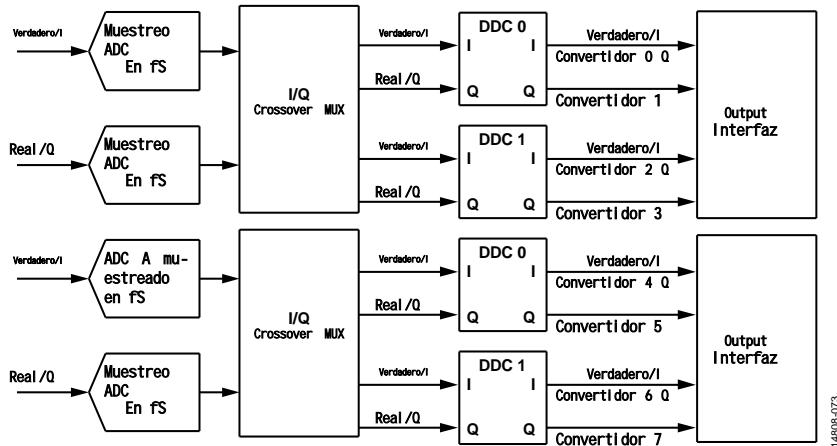

| Selección de entrada DDC I/O                         | 33 | Funciones accesibles SPI                                    | 71 |

| Selección de salida DDC I/O                          | 33 | Mapa de memoria                                             | 72 |

| Descripción general de DDC                           | 33 | Leer la tabla de registro de mapeo de memoria               | 72 |

| Conversión de frecuencia                             | 39 | Tabla de registros mapeados en memoria-Detalles             | 73 |

| Visión general                                       | 39 | Información de la solicitud                                 | 95 |

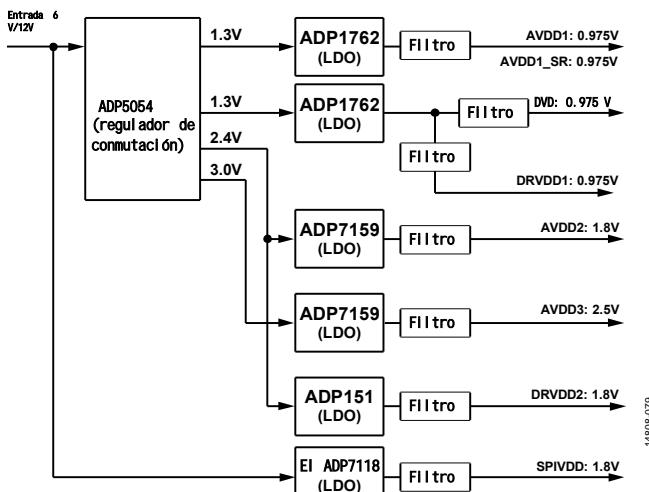

| DDC NCO y pérdidas del mezclador y SFDR              | 40 | Recomendaciones de fuente de alimentación                   | 95 |

| Oscilador de control numérico                        | 40 | Recomendaciones para disipadores de calor de aluminio       | 95 |

| Filtro FIR                                           | 42 | al mohadillas expuestas                                     | 95 |

| Visión general                                       | 42 | AVDD1_SR (pin 64) y AGND_SR (pin 63 y pin 63)               | 95 |

|                                                      |    | 67)                                                         | 95 |

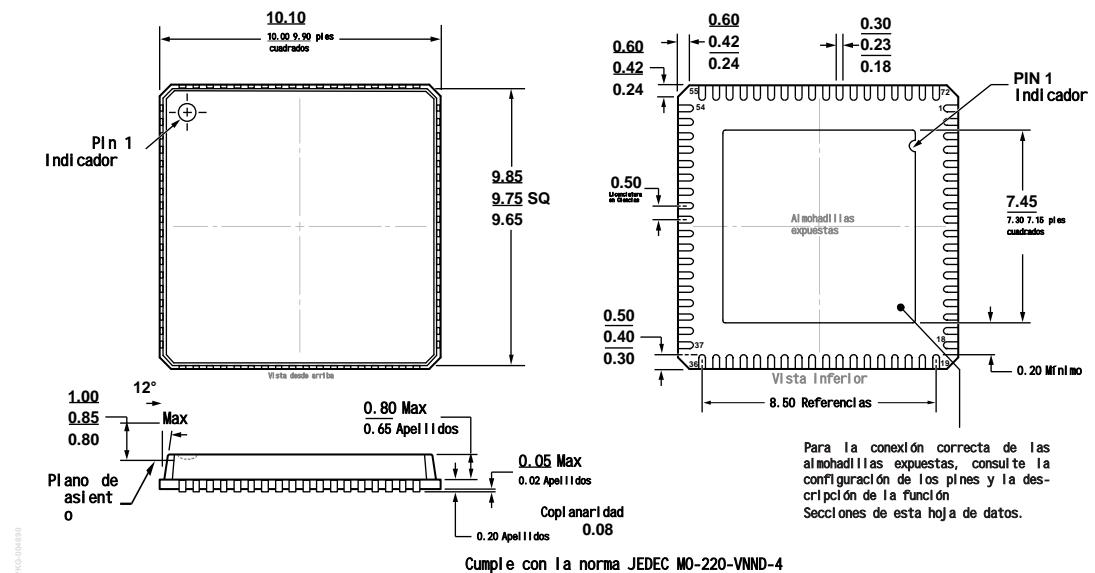

|                                                      |    | Dimensiones exteriores                                      | 96 |

|                                                      |    | Guía de pedido                                              | 96 |

**Historial de revisiones****2/2018-Rev. A a la versión B**

|                                                                                                                                                                                 |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Cambiar el título del documento de convertidor analógico a digital doble de 14 bits, 1.25GSPS, 1.2V/2.5V a convertidor analógico a digital de 14 bits, 500 MSPS, JESD204B ..... | Universal es |

| Cambiar a una tabla 10 .....                                                                                                                                                    | 14           |

| Sección de diodo de temperatura móvil .....                                                                                                                                     | 28           |

**Diciembre 2017-Rev. 0 A la versión A**

|                                                                                                                                                                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Cambiar 1.8V p-p a 1.80V p-p .....                                                                                                                                    | A través de |

| Cambios en el diagrama 1 .....                                                                                                                                        | 1           |

| Cambios en la nota 3 al final del cuadro 2 .....                                                                                                                      | 7           |

| Cambios en los parámetros de salida lógica (FD_A, FD_B, FD_C, FD_D) y en los parámetros de salida digital (SERDOUTAB $\pm$ /SERDOUTCD $\pm$ , x=0 ó 1), tabla 5 ..... | 9           |

| Cambios en los parámetros de salida y los parámetros de tiempo de activación, tabla 6 .....                                                                           | 10          |

| CAMBIOS EN LAS FORMAS 9 .....                                                                                                                                         | 12          |

| CAMBIOS EN LAS FORMAS 10 .....                                                                                                                                        | 13          |

| Cambios a las figuras 18, 19, 20 y 23 .....                                                                                                                           | 17          |

| CAMBIOS EN LA Figura 47 Y LA Figura 48 .....                                                                                                                          | 22          |

| Cambios en la sección de consideraciones de entrada analógica y la sección de configuración de entrada diferencial .....                                              | 24          |

| CAMBIOS EN LAS FORMAS 11 .....                                                                                                                                        | 25          |

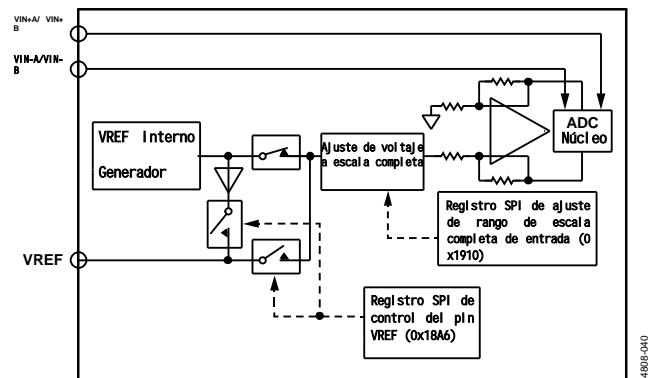

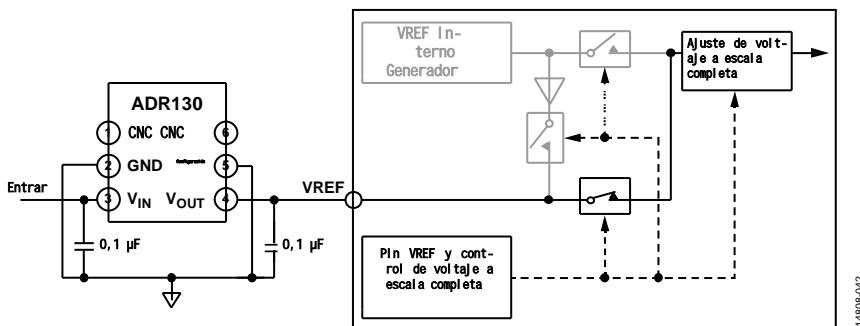

| Cambios en la sección de referencia de tensión, la sección de calibración de desplazamiento de CC y el diagrama 62 .....                                              | 26          |

| Ciclo de trabajo del reloj Cambios en la sección de consideraciones y la figura 65 .....                                                                              | 27          |

| Agregue la parte de detección de reloj de entrada .....                                                                                                               | 27          |

| Cambios en la sección del diodo de temperatura ..                                                                                                                     | 28          |

| Cambiar la sección de descripción general a la sección de descripción general .....                                                                                   | 39          |

|                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Cambios en la sección de descripción general .....                                                                                                                                                        | 42 |

| Cambiado a la sección de bucle de bloqueo de fase (PLL) .....                                                                                                                                             | 54 |

| Cambiar a una tabla 26 .....                                                                                                                                                                              | 56 |

| CAMBIOS EN LAS FORMAS 27 .....                                                                                                                                                                            | 57 |

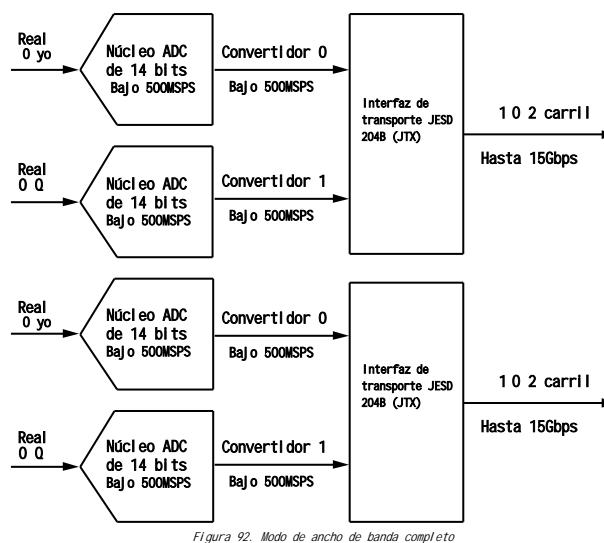

| Cambios en el ejemplo 2: ADC con opción DDC (dos ADC por par más dos secciones DDC y figura 92) ..                                                                                                        | 58 |

| Se han añadido una sección de cálculo de retardo de ejemplo, una sección de configuración de ejemplo 1, una sección de configuración de ejemplo 2, la tabla 29 y la tabla 30; Renumeración en orden ..... | 60 |

| Se agregó la sección de retardo determinista, subclase 0 operación                                                                                                                                        |    |

| Sección, sección de operación de subclase 1, sección de requerimiento de retardo determinista, sección de establecimiento de registro de retardo determinista y figura 94; Renumeración en orden          | 61 |

| Se añadió la Figura 95 y la Figura 96 .....                                                                                                                                                               | 62 |

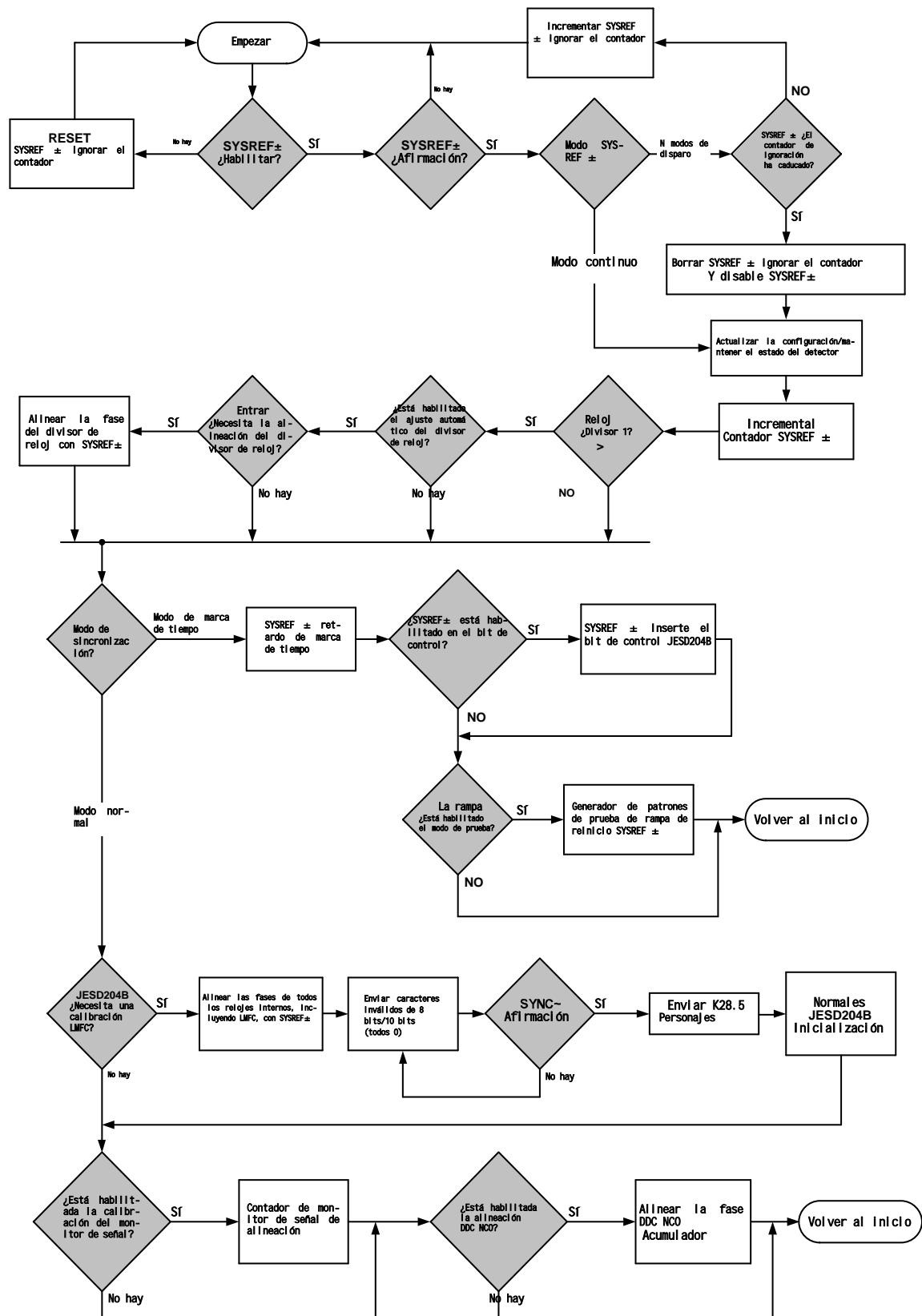

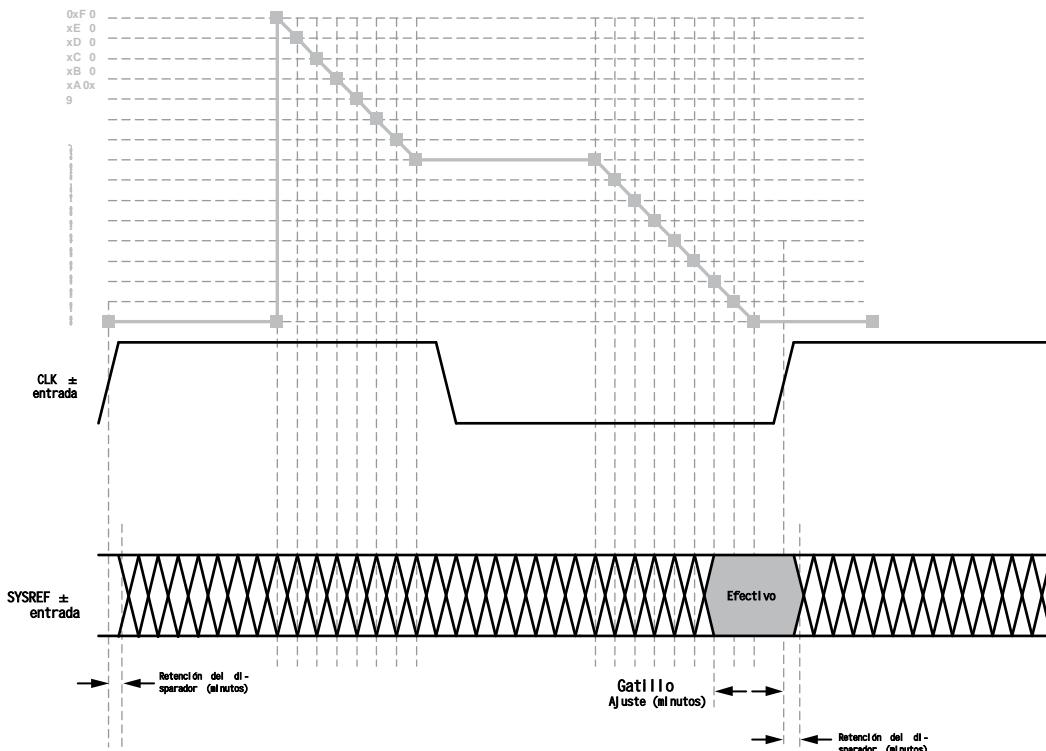

| Se agregaron parte de sincronización multichip, parte de modo normal, parte de modo de marca de tiempo, figura 97 .....                                                                                   | 63 |

| Añadir gráficos 98 .....                                                                                                                                                                                  | 64 |

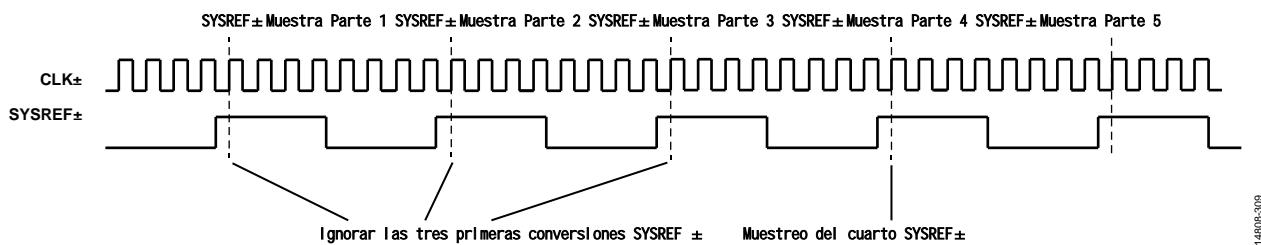

| Se añadieron la sección de entrada SYSREF $\pm$ , la sección de características de control SYSREF $\pm$ , la Figura 99, la Figura 100, la Figura 101 y la Figura 102 .....                                | 65 |

| Cambios en la sección de monitor de ventana SYSREF $\pm$ SETT/HOLD .....                                                                                                                                  | 66 |

| Cambios en la sección del modo de prueba del ADC ..                                                                                                                                                       | 68 |

| Se suprime la sección de resumen del registro y el cuadro 38; Renumeración en orden .....                                                                                                                 | 69 |

| Cambios en la sección de la tabla de registros de lectura de mapas de memoria .....                                                                                                                       | 72 |

| CAMBIOS EN LAS FORMAS 39 .....                                                                                                                                                                            | 73 |

| CAMBIOS EN LA SECCIÓN DE RECOMENDACIÓN DE LA FUENCIA Y 106 .....                                                                                                                                          | 95 |

**10/2016-Revisión 0: versión inicial**

## INSTRUCCION GENERAL

El AD9694 es un convertidor analógico a digital (ADC) de cuatro canales, 14 bits y 500 MSPS. El dispositivo cuenta con una memoria intermedia en el chip y un circuito de muestra y retención, diseñado para un bajo consumo de energía, tamaño pequeño y facilidad de uso. El dispositivo está diseñado para muestrear señales analógicas de ancho de banda de hasta 1,4 GHz. El AD9694 está optimizado para un amplio ancho de banda de entrada, alta frecuencia de muestreo, excelente linealidad y bajo consumo de energía en un paquete pequeño.

El núcleo ADC de cuatro vías utiliza una arquitectura de tubería diferencial de múltiples etapas e integra la lógica de corrección de errores de salida. Cada ADC tiene una amplia entrada de ancho de banda que admite una variedad de rangos de entrada seleccionables por el usuario. La referencia de voltaje integrada simplifica las consideraciones de diseño.

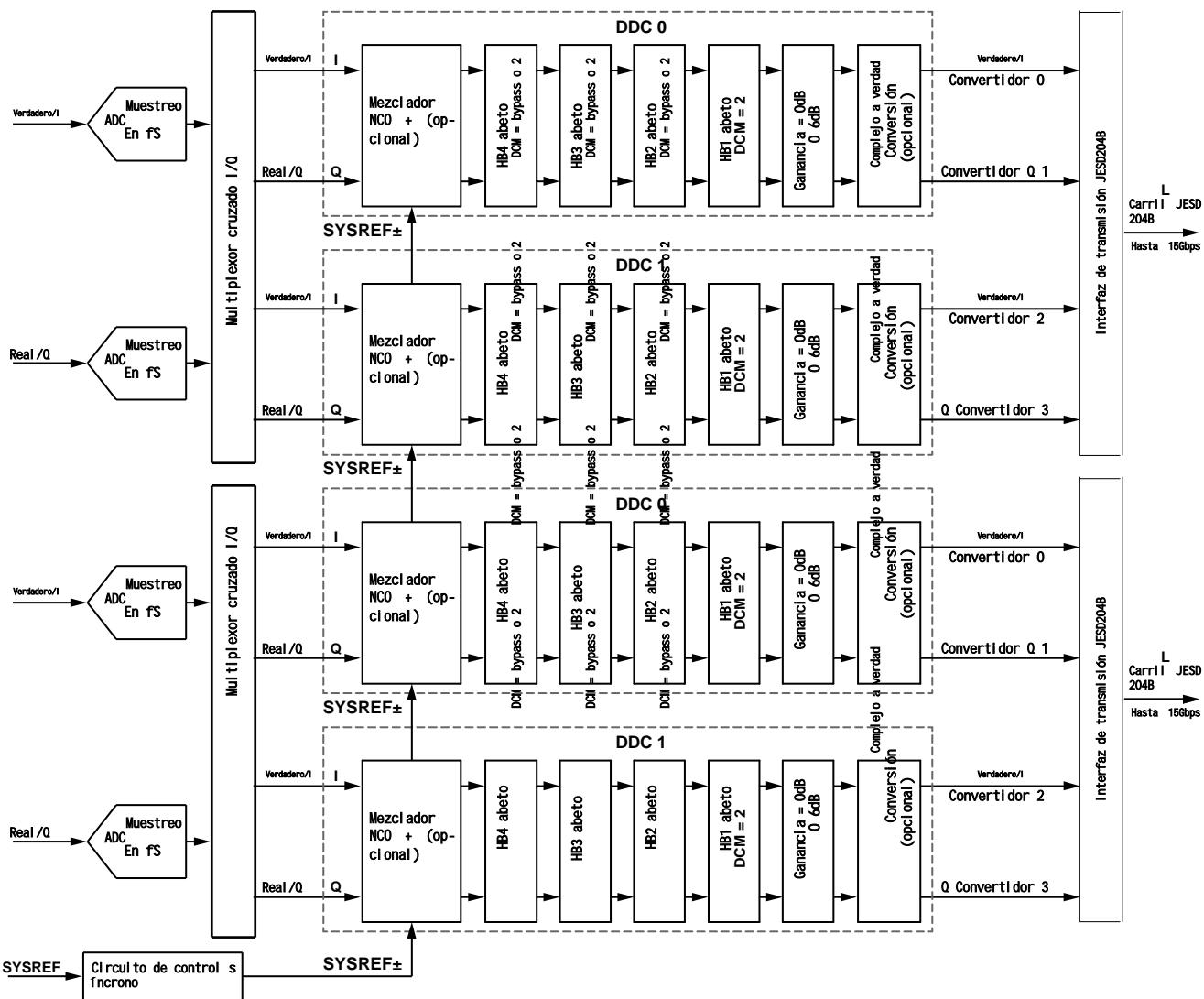

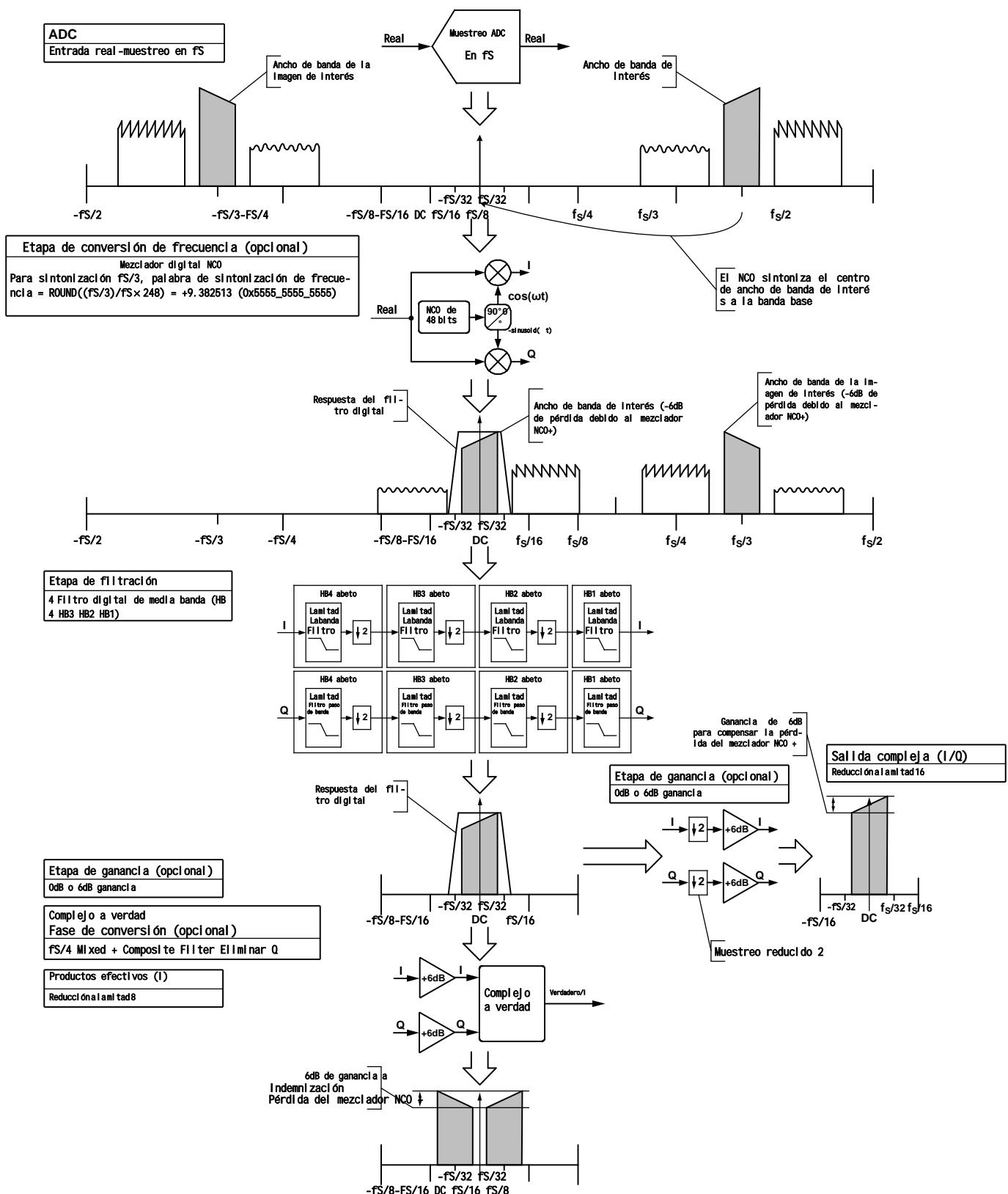

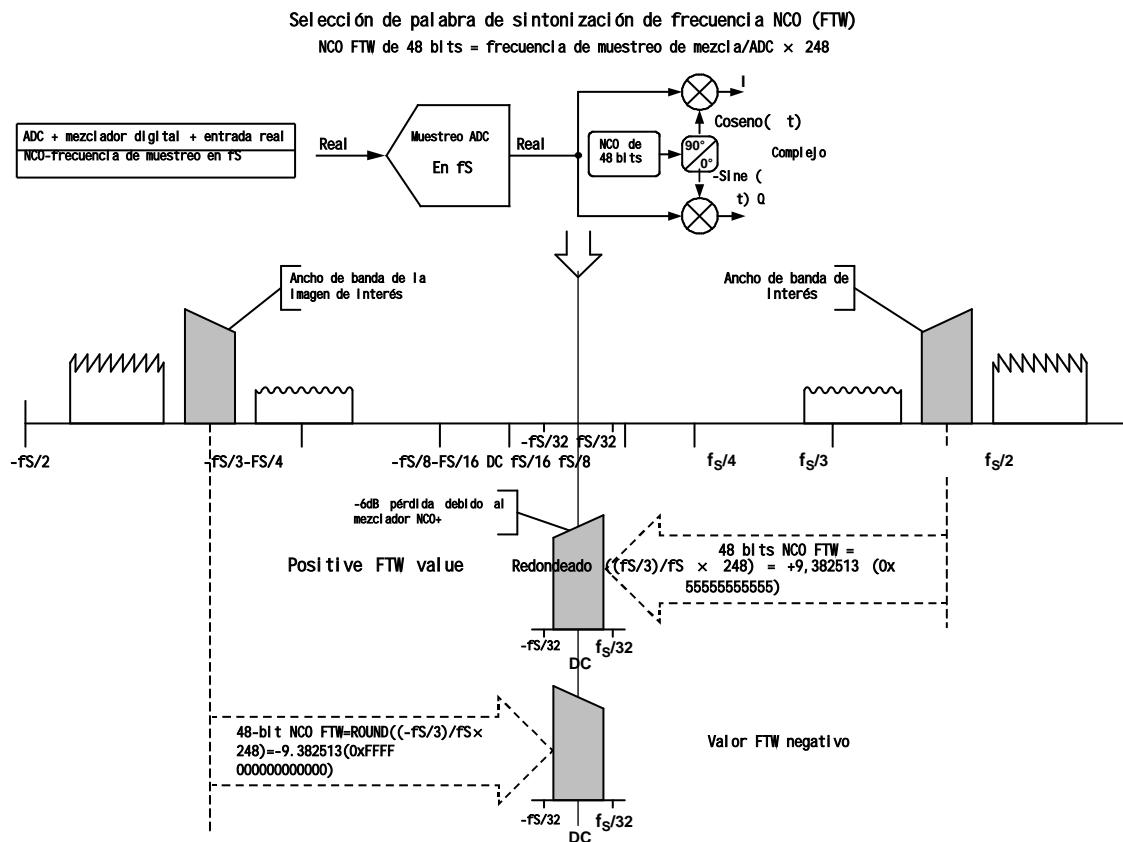

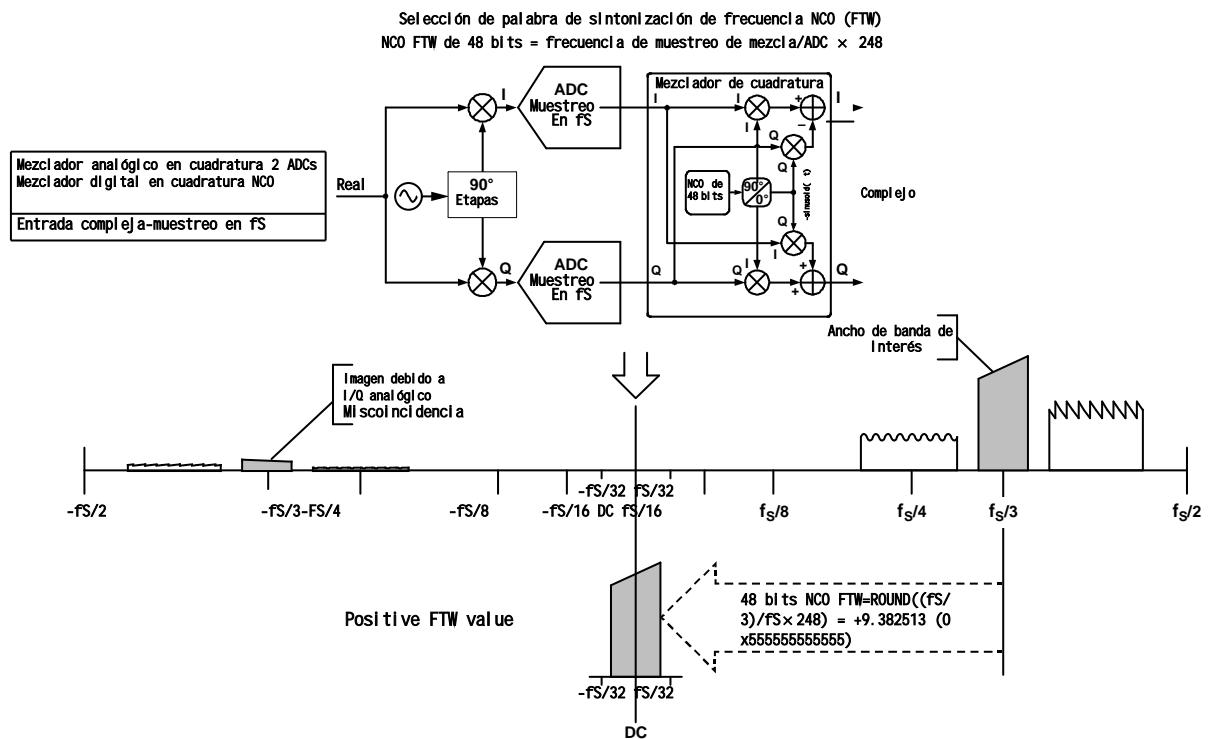

La entrada analógica y la señal de reloj son entradas diferenciales. Cada par de salidas de datos de ADC está conectado internamente a dos DDC a través de un mux cruzado. Cada DDC consta de hasta cinco etapas de procesamiento de señal en cascada: un convertidor de frecuencia de 48 bits, NCO y hasta cuatro filtros de decimación de media banda.

Además del módulo DDC, el AD9694 tiene una variedad de características que simplifican las funciones de control automático de ganancia (AGC) en los receptores de comunicaciones. El detector de umbral programable permite monitorear la potencia de la señal de entrada usando los bits de salida de detección rápida del ADC. Si el nivel de la señal de entrada excede el umbral programable, el indicador de detección rápida se vuelve alto. Debido a que este indicador de umbral tiene una latencia baja, el usuario puede reducir rápidamente la ganancia del sistema para evitar condiciones fuera de rango en la entrada del ADC.

El usuario puede configurar cada par de salidas del receptor de frecuencia intermedia (IF) en uno o ambos canales de la salida serializada de alta velocidad basada en la subclase 1 JESD204B, dependiendo de la relación de decimación del dispositivo lógico de recepción y la velocidad de canal aceptable. Soporta la sincronización de múltiples dispositivos a través de los pines de entrada SYSREF $\pm$ , SYNCINB $\pm$ AB y SYNCINB $\pm$ CD. El AD9694 cuenta con opciones flexibles de apagado para ahorrar energía significativamente cuando sea necesario. Todas estas funciones se pueden programar usando un SPI de 3 hilos con soporte de 1.8V.

El AD9694 utiliza un LFCSP sin plomo de 72 pines con un rango de temperatura de unión especificado de -40° C a +105° C. El producto puede estar protegido por una o más patentes estadounidenses o internacionales.

## Destacados del producto

1. Bajo consumo de energía por canal.

2. La velocidad de canal JESD204B es compatible con hasta 15 Gbps.

3. El amplio ancho de banda de potencia completa admite el muestreo de frecuencia intermedia de señales de hasta 1,4 GHz.

4. La entrada de almacenamiento intermedio simplifica el diseño y la implementación del filtro.

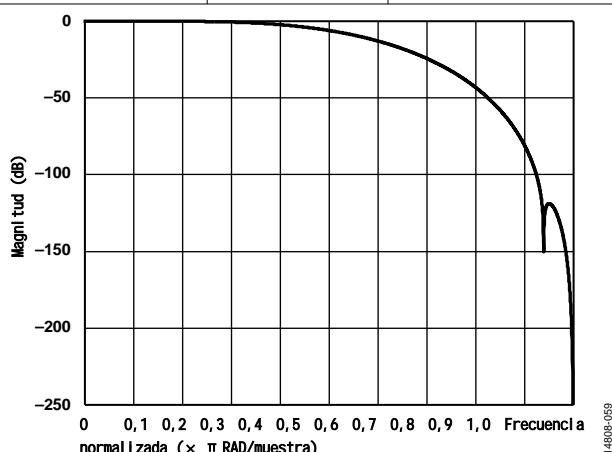

5. Cuatro filtros de decimación de banda ancha integrados y un módulo de oscilador controlado numéricamente (NCO) que admite receptores multibanda.

6. Detección rápida programable fuera de rango.

7. Diodos de temperatura en chip para la gestión térmica del sistema.

## Especificación

### Especificaciones DC

AVDD1 = 0,975 V, AVDD1\_SR = 0,975 V, AVDD2 = 1,8 V, AVDD3 = 2,5 V, DVDD = 0,975 V, DRVDD1 = 0,975 V, DRVDD2 = 1,8 V, SPIVDD = 1,8 V, 500 MSPS, divisor de reloj = 4, entrada diferencial a escala completa de 1,80 V p-p, referencia interna de 0,5 V, AIN = 1,0 dBFS, ajuste SPI predeterminado, a menos que se indique lo contrario. Las especificaciones mínimas y máximas están garantizadas a lo largo de todo el rango de temperatura de unión de funcionamiento (TJ) de -40° C a +105° C. Las especificaciones típicas representan el rendimiento a TJ = 50 ° C (TA = 25 ° C).

Cuadro 1.

| Parámetros                                                                        | Mínimo | Tipo de              | Max  | Unidad              |

|-----------------------------------------------------------------------------------|--------|----------------------|------|---------------------|

| Resolución                                                                        | 14     |                      |      | Bits                |

| Precisión                                                                         |        |                      |      |                     |

| Sin código perdido                                                                |        | Garantía             |      |                     |

| Error de compensación                                                             | 0      |                      |      | % FSR               |

| Coincidencia de desplazamiento                                                    | 0      |                      |      | % FSR               |

| Error de ganancia                                                                 | -5.0   |                      | +5.0 | % FSR               |

| Coincidencia de ganancia                                                          | 1.0    |                      | 3.7  | % FSR               |

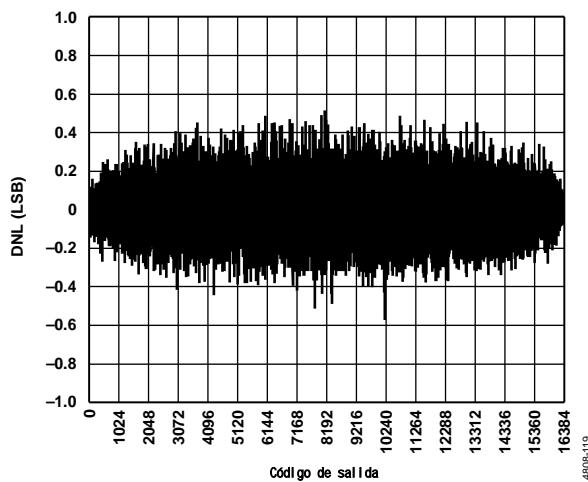

| No linealidad diferencial                                                         | -0.7   | ±0.4                 | +0.7 | LSB                 |

| No linealidad integral                                                            | -5.1   | ±1.0                 | +5.1 | LSB                 |

| Error de desplazamiento de derivada de temperatura                                | 8      |                      |      | ppm/°C              |

| Error de ganancia                                                                 | 214    |                      |      | ppm/°C              |

| Referencia de voltaje interno                                                     | 0.5    |                      |      | V                   |

| Ruido de referencia de entrada                                                    | 2.6    |                      |      | LSB RMS             |

| Entradas analógicas                                                               |        |                      |      |                     |

| Rango de voltaje de entrada diferencial (programable) Voltaje de modo común (VCM) | 1.44   | 1.80<br>1.34<br>1.75 | 2.16 | V p-p V pF Ω<br>GHz |

| Condensador de entrada diferencial 1                                              |        | 200                  |      |                     |

| Resistencia de entrada diferencial                                                |        | 1.4                  |      |                     |

| Ancho de banda de potencia completo de entrada analógica                          |        |                      |      |                     |

| Fuente de alimentación                                                            |        |                      |      |                     |

| AVDD1                                                                             | 0.95   | 0.975                | 1.00 | V                   |

| AVDD1_SR                                                                          | 0.95   | 0.975                | 1.00 | V                   |

| AVDD2                                                                             | 1.71   | 1.8                  | 1.89 | V                   |

| AVDD3                                                                             | 2.44   | 2.5                  | 2.56 | V                   |

| DVDD                                                                              | 0.95   | 0.975                | 1.00 | V                   |

| DRVDD1                                                                            | 0.95   | 0.975                | 1.00 | V                   |

| DRVDD2                                                                            | 1.71   | 1.8                  | 1.89 | V                   |

| SpiVDD                                                                            | 1.71   | 1.8                  | 1.89 | V                   |

| I <sub>AVDD1</sub>                                                                | 319    | 482                  |      | Cableado            |

| I <sub>AVDD1_SR</sub>                                                             | 21     | 53                   |      | Cableado            |

| I <sub>AVDD2</sub>                                                                | 438    | 473                  |      | Cableado            |

| I <sub>AVDD3</sub>                                                                | 87     | 103                  |      | Cableado            |

| I <sub>DVDD<sup>2</sup></sub>                                                     | 121    | 180                  |      | Cableado            |

| I <sub>DRVDD1<sup>1</sup></sub>                                                   | 162    | 207                  |      | Cableado            |

| I <sub>DRVDD2<sup>1</sup></sub>                                                   | 23     | 29                   |      | Cableado            |

| I <sub>SPIVDD</sub>                                                               | 1      | 1.6                  |      | Cableado            |

| Consumo de electricidad                                                           |        |                      |      |                     |

| Consumo total de energía (incluido el controlador de salida) <sup>2</sup>         | 1.66   | 2.07                 |      | W                   |

| Dissipación de corte de energía                                                   | 325    |                      |      | mW                  |

| En espera <sup>3</sup>                                                            | 1.20   |                      |      | W                   |

<sup>1</sup> Todos los carriles están en funcionamiento. El consumo de energía en el DRVDD1 varía con la velocidad de canal y el número de canales utilizados.

<sup>2</sup> Modo de ancho de banda completo.

<sup>3</sup> El modo de espera está controlado por el SPI.

## Especificaciones AC

AVDD1=0.975V, AVDD1\_SR=0.975V, AVDD2=1.8V, AVDD3=2.5V, DVDD=0.975V, DRVDD1=0.975V, DRVDD2=1.8V, SPI VDD=1.8V, frecuencia de muestreo máxima especificada, divisor de reloj = 4, entrada diferencial a escala completa de 1.80V p-p, referencia interna de 0.5V, AIN=1.0dBFS, ajuste SPI predeterminado, a menos que se indique lo contrario. Las especificaciones mínimas y máximas están garantizadas a lo largo de todo el rango de temperatura de unión de funcionamiento (TJ) de -40° C a +105° C. Las especificaciones típicas representan el rendimiento a TJ = 50 ° C (TA = 25 ° C).

Tabla 2.500 ESPECIFICACIONES DE MSPS AC

| Parámetros                                                      | Entrada analógica a escala completa = 1.44 V p-p |        | Entrada analógica a escala completa = 1.80 V p-p |      | Entrada analógica a escala completa = 2.16 V p-p |     | Unidad  |        |      |

|-----------------------------------------------------------------|--------------------------------------------------|--------|--------------------------------------------------|------|--------------------------------------------------|-----|---------|--------|------|

|                                                                 | Tipo                                             | minimo | Max                                              | Tipo | minimo                                           | Max | Tipo    | minimo | Max  |

| Entrada analógica a escala completa                             | 1.44                                             |        | 1.80                                             |      | 2.16                                             |     | V p-p   |        |      |

| Densidad de ruido 2                                             | -149.7                                           |        | -151.5                                           |      | -153.0                                           |     | dBFS/Hz |        |      |

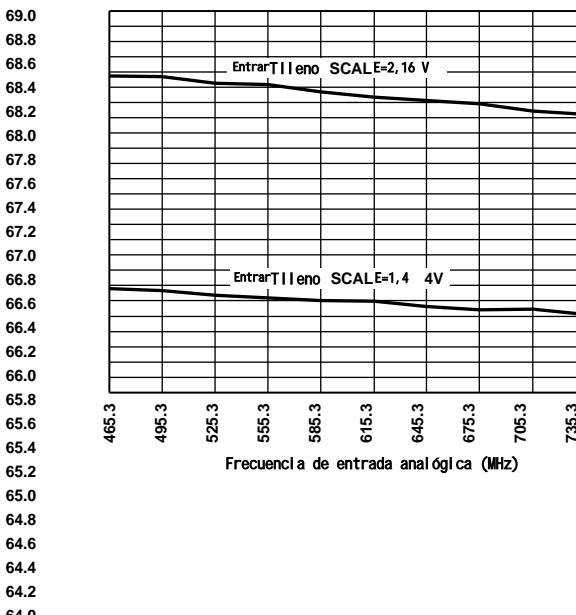

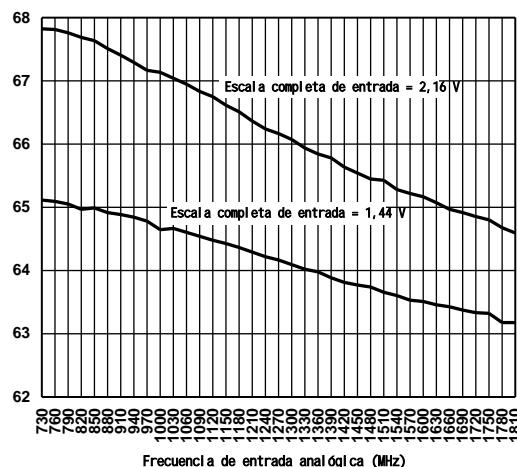

| Relación señal a ruido (SNR) 3 f <sub>IN</sub> =10 MHz          | 65.4                                             |        | 67.1                                             |      | 68.4                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 155 MHz                                       | 65.3                                             |        | 67.0                                             |      | 68.3                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 305 MHz                                       | 65.2                                             |        | 66.8                                             |      | 68.0                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 450 MHz                                       | 65.0                                             |        | 66.6                                             |      | 67.8                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 765 MHz                                       | 64.8                                             |        | 66.5                                             |      | 67.5                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 985 MHz                                       | 64.5                                             |        | 66.0                                             |      | 66.9                                             |     |         |        | dBFS |

| Relación señal /ruido/distorsión (SNR)                          | 65.3                                             |        | 67.0                                             |      | 68.2                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 10 MHz f <sub>IN</sub> = 155 MHz              | 65.2                                             |        | 66.8                                             |      | 67.9                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 305 MHz                                       | 65.1                                             |        | 66.6                                             |      | 67.6                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 450 MHz                                       | 65.0                                             |        | 66.4                                             |      | 67.3                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 765 MHz                                       | 64.7                                             |        | 66.1                                             |      | 66.9                                             |     |         |        | dBFS |

| f <sub>IN</sub> = 985 MHz                                       | 64.2                                             |        | 65.5                                             |      | 66.2                                             |     |         |        | dBFS |

| Número de bits significativos (EN-OB) f <sub>IN</sub> =10 MHz   | 10.5                                             |        | 10.8                                             |      | 11.0                                             |     |         |        | Bits |

| f <sub>IN</sub> = 155 MHz                                       | 10.5                                             |        | 10.8                                             |      | 10.9                                             |     |         |        | Bits |

| f <sub>IN</sub> = 305 MHz                                       | 10.5                                             |        | 10.7                                             |      | 10.9                                             |     |         |        | Bits |

| f <sub>IN</sub> = 450 MHz                                       | 10.5                                             |        | 10.7                                             |      | 10.8                                             |     |         |        | Bits |

| f <sub>IN</sub> = 765 MHz                                       | 10.4                                             |        | 10.6                                             |      | 10.8                                             |     |         |        | Bits |

| f <sub>IN</sub> = 985 MHz                                       | 10.3                                             |        | 10.6                                             |      | 10.7                                             |     |         |        | Bits |

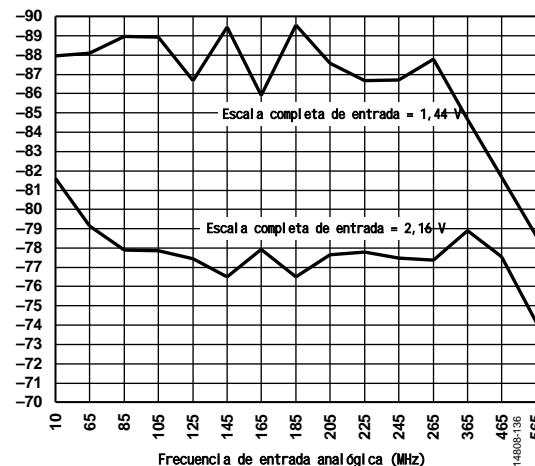

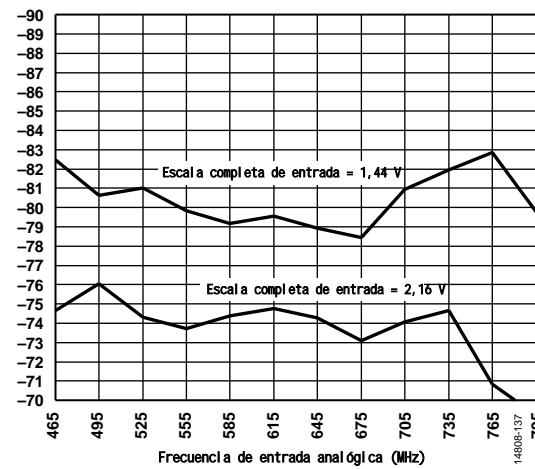

| Rango dinámico libre de espurias (SFDR) f <sub>IN</sub> =10 MHz | 89                                               |        | 90                                               |      | 80                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 155 MHz                                       | 89                                               |        | 85                                               |      | 77                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 305 MHz                                       | 82                                               |        | 82                                               |      | 78                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 450 MHz                                       | 82                                               |        | 83                                               |      | 77                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 765 MHz                                       | 77                                               |        | 75                                               |      | 72                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 985 MHz                                       | 82                                               |        | 79                                               |      | 76                                               |     |         |        | dBFS |

| Rango dinámico sin parásitos (SFDR)                             | 94                                               |        | 94                                               |      | 86                                               |     |         |        | dBFS |

| f <sub>IN</sub> =10 MHz a 3 dBFS f <sub>IN</sub> =155 MHz       | 94                                               |        | 90                                               |      | 82                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 305 MHz                                       | 89                                               |        | 90                                               |      | 83                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 450 MHz                                       | 87                                               |        | 86                                               |      | 84                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 765 MHz                                       | 82                                               |        | 80                                               |      | 77                                               |     |         |        | dBFS |

| f <sub>IN</sub> = 985 MHz                                       | 85                                               |        | 82                                               |      | 79                                               |     |         |        | dBFS |

| Peor armónico, aleta secundaria o tercera = 10 MHz              | -89                                              |        | -90                                              |      | -80                                              |     |         |        | dBFS |

| f <sub>IN</sub> = 155 MHz                                       | -89                                              |        | -85                                              |      | -77                                              |     |         |        | dBFS |

| f <sub>IN</sub> = 305 MHz                                       | -82                                              |        | -82                                              |      | -78                                              |     |         |        | dBFS |

| f <sub>IN</sub> = 450 MHz                                       | -82                                              |        | -83                                              |      | -77                                              |     |         |        | dBFS |

| f <sub>IN</sub> = 765 MHz                                       | -77                                              |        | -75                                              |      | -72                                              |     |         |        | dBFS |

| f <sub>IN</sub> = 985 MHz                                       | -82                                              |        | -79                                              |      | -76                                              |     |         |        | dBFS |

| Parámetro 1                                                                                                                                                                                                                                | Entrada analógica a escala completa =<br>1.44 V p-p<br>Tipo mínimo | Max | Entrada analógica a escala completa =<br>1.80 V p-p Tipo mínimo | Max | Entrada analógica a escala completa =<br>2.16 V p-p<br>Tipo mínimo | Max | Unidad |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----------------------------------------------------------------|-----|--------------------------------------------------------------------|-----|--------|

| Segundo o tercer peor armónico a 3 dBFS<br>$f_{IN} = 10 \text{ MHz}$ $f_{IN} = 155 \text{ MHz}$<br>$f_{IN} = 305 \text{ MHz}$<br>$f_{IN} = 450 \text{ MHz}$<br>$f_{IN} = 765 \text{ MHz}$<br>$f_{IN} = 985 \text{ MHz}$                    | -94<br>-94<br>-89<br>-87<br>-82<br>-85                             |     | -94<br>-90<br>-90<br>-86<br>-80<br>-82                          |     | -86<br>-82<br>-83<br>-84<br>-77<br>-79                             |     | dBFS   |

| Peor de los demás, excluyendo el segundo o tercer armónico<br>$f_{IN} = 10 \text{ MHz}$ $f_{IN} = 155 \text{ MHz}$<br>$f_{IN} = 305 \text{ MHz}$<br>$f_{IN} = 450 \text{ MHz}$<br>$f_{IN} = 765 \text{ MHz}$<br>$f_{IN} = 985 \text{ MHz}$ | -96<br>-97<br>-97<br>-95<br>-92<br>-90                             |     | -98<br>-97<br>-98<br>-96<br>-91<br>-89                          | -86 | -99<br>-97<br>-97<br>-96<br>-88<br>-86                             |     | dBFS   |

| Distorsión de intermodulación de dos tonos (IMD), AIN1 y AIN2 = -7 dBFS<br>$f_{IN1} = 154 \text{ MHz}$ , $f_{IN2} = 157 \text{ MHz}$ $f_{IN1} = 302 \text{ MHz}$ , $f_{IN2} = 305 \text{ MHz}$                                             | -93<br>-90                                                         |     | -90<br>-90                                                      |     | -84<br>-84                                                         |     | dBFS   |

| Crosstalk 4                                                                                                                                                                                                                                | 82                                                                 |     | 82                                                              |     | 82                                                                 |     | dB     |

| Ancho de banda de potencia completo 5                                                                                                                                                                                                      | 1.4                                                                |     | 1.4                                                             |     | 1.4                                                                |     | GHz    |

<sup>1</sup> Para obtener información detallada sobre la definición y cómo completar estas pruebas, consulte la Nota de aplicación AN-835, Comprensión de las pruebas y evaluación de ADC de alta velocidad.

<sup>2</sup> La densidad de ruido se mide a una frecuencia de entrada analógica baja (30 MHz).

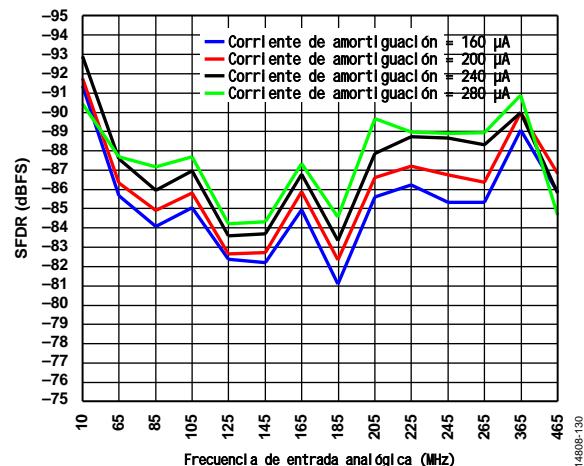

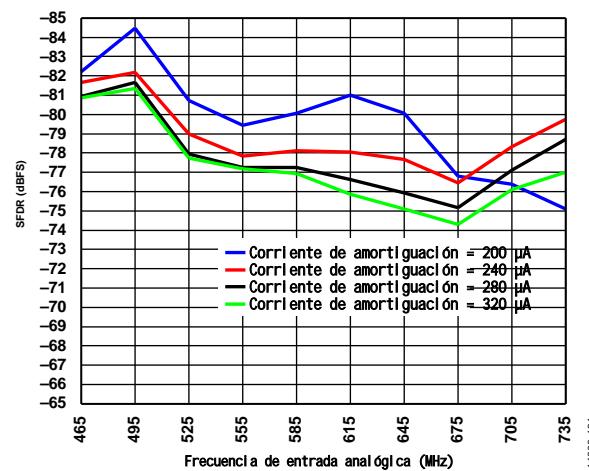

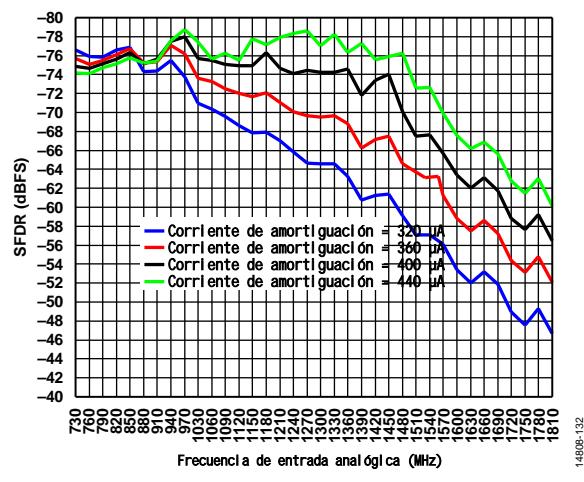

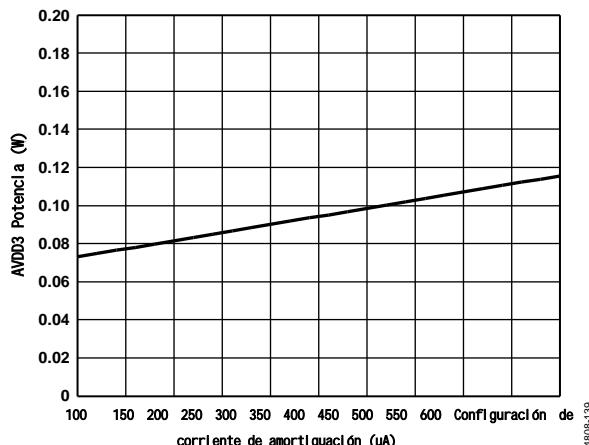

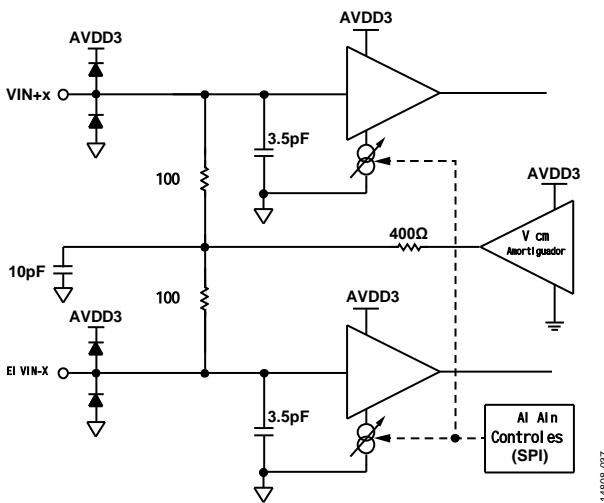

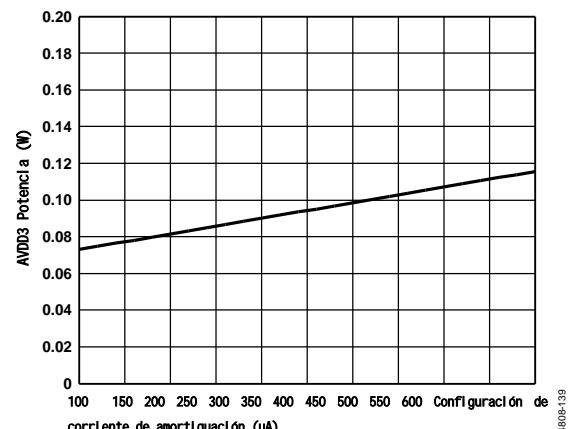

<sup>3</sup> Véase la Tabla 11 para los ajustes recomendados para el ajuste de la corriente de amortiguación.

<sup>4</sup> La diafonía se mide a 155 MHz con una entrada analógica de -1,0 dBFS en un canal y ninguna entrada en los canales adyacentes.

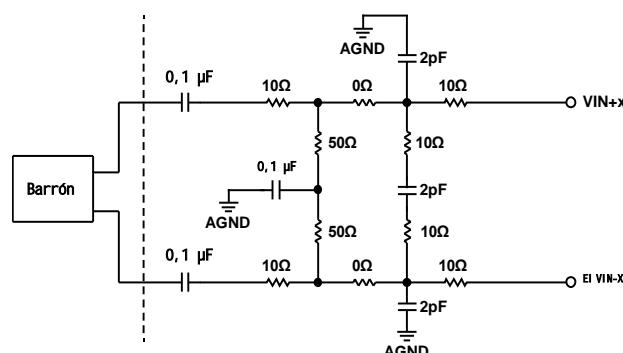

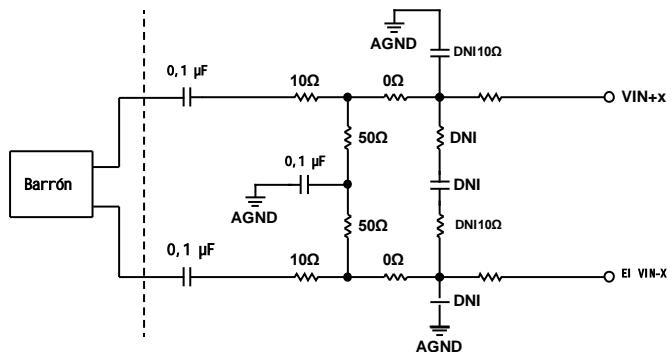

<sup>5</sup> Se midió con el circuito mostrado en la Figura 56.

Tabla 3.600 ESPECIFICACIONES CA MSPS, ENTRADA ANALÓGICA = 1.80 V p-p

| Entrada analógica a escala completa                                 | 1.80 | V p-p |

|---------------------------------------------------------------------|------|-------|

| Relación señal a ruido (SNR) $f_{IN}=10 \text{ MHz}$                | 66.6 | dBFS  |

| $f_{IN} = 155 \text{ MHz}$                                          | 67   | dBFS  |

| $f_{IN} = 305 \text{ MHz}$                                          | 66.8 | dBFS  |

| $f_{IN} = 450 \text{ MHz}$                                          | 66.4 | dBFS  |

| $f_{IN} = 765 \text{ MHz}$                                          | 66   | dBFS  |

| $f_{IN} = 985 \text{ MHz}$                                          | 65.5 | dBFS  |

| Relación señal a ruido y distorsión (SINAD) $f_{IN}=10 \text{ MHz}$ | 66.5 | dBFS  |

| $f_{IN} = 155 \text{ MHz}$                                          | 66.8 | dBFS  |

| $f_{IN} = 305 \text{ MHz}$                                          | 66.5 | dBFS  |

| $f_{IN} = 450 \text{ MHz}$                                          | 66.3 | dBFS  |

| $f_{IN} = 765 \text{ MHz}$                                          | 65.4 | dBFS  |

| $f_{IN} = 985 \text{ MHz}$                                          | 64.8 | dBFS  |

| Rango dinámico libre de espurias (SFDR) $f_{IN}=10 \text{ MHz}$     | 86   | dBFS  |

| $f_{IN} = 155 \text{ MHz}$                                          | 81   | dBFS  |

| $f_{IN} = 305 \text{ MHz}$                                          | 81   | dBFS  |

| $f_{IN} = 450 \text{ MHz}$                                          | 84   | dBFS  |

| $f_{IN} = 765 \text{ MHz}$                                          | 76   | dBFS  |

| $f_{IN} = 985 \text{ MHz}$                                          | 75   | dBFS  |

| Parámetro 1                                        | Mínimo | Tipo de | Max | Unidad |

|----------------------------------------------------|--------|---------|-----|--------|

| Peor armónico, aleta secundaria o tercera = 10 MHz | –86    |         |     | dBFS   |

| $f_{IN} = 155$ MHz                                 | –81    |         |     | dBFS   |

| $f_{IN} = 305$ MHz                                 | –81    |         |     | dBFS   |

| $f_{IN} = 450$ MHz                                 | –84    |         |     | dBFS   |

| $f_{IN} = 765$ MHz                                 | –76    |         |     | dBFS   |

| $f_{IN} = 985$ MHz                                 | –75    |         |     | dBFS   |

<sup>1</sup> Para obtener información detallada sobre la definición y cómo completar estas pruebas, consulte la Nota de aplicación AN-835, Comprensión de las pruebas y evaluación de ADC de alta velocidad.

Tabla 4. Consumo de energía de 600 MSPS

| Parámetros                                                   | Mínimo | Tipo de | Max  | Unidad  |

|--------------------------------------------------------------|--------|---------|------|---------|

| Fuente de alimentación                                       |        |         |      |         |

| AVDD1                                                        | 0.95   | 0.975   | 1.00 | V       |

| AVDD1_SR                                                     | 0.95   | 0.975   | 1.00 | V       |

| AVDD2                                                        | 1.71   | 1.8     | 1.89 | V       |

| AVDD3                                                        | 2.44   | 2.5     | 2.56 | V       |

| DVD                                                          | 0.95   | 0.975   | 1.00 | V       |

| DRVDD1                                                       | 0.95   | 0.975   | 1.00 | V       |

| DRVDD2                                                       | 1.71   | 1.8     | 1.89 | V       |

| Spivd                                                        | 1.71   | 1.8     | 1.89 | V       |

| $I_{AVDD1}$                                                  |        | 352     | 513  | Caballo |

| $I_{AVDD1\_SR}$                                              |        | 23      | 55   | Caballo |

| $I_{AVDD2}$                                                  |        | 443     | 478  | Caballo |

| $I_{AVDD3}$                                                  |        | 87      | 104  | Caballo |

| $I_{DVD}$ <sup>1</sup>                                       |        | 146     | 200  | Caballo |

| $I_{DRVDD1}$ <sup>2</sup>                                    |        | 183     | 235  | Caballo |

| $I_{DRVDD2}$ <sup>2</sup>                                    |        | 23      | 28   | Caballo |

| $I_{SPIVDD}$                                                 |        | 1       | 1.6  | Caballo |

| Consumo de electricidad                                      |        |         |      |         |

| Consumo total de energía (incluido el controlador de salida) | 1.75   |         | 2.16 | W       |

<sup>1</sup> Modo de ancho de banda completo.

<sup>2</sup> Todos los carriles están en funcionamiento. El consumo de energía en el DRVDD1 varía con la velocidad de canal y el número de canales utilizados.

## Especificaciones digitales

AVDD1 = 0,975 V, AVDD1\_SR = 0,975 V, AVDD2 = 1,8 V, AVDD3 = 2,5 V, DVDD = 0,975 V, DRVDD1 = 0,975 V, DRVDD2 = 1,8 V, SPIVDD = 1,8 V, 500 MSPS, divisor de reloj = 4, entrada diferencial a escala completa de 1,80 V p-p, referencia interna de 0,5 V, AIN = 1,0 dBFS, ajuste SPI predeterminado, a menos que se indique lo contrario. Las especificaciones mínimas y máximas están garantizadas a lo largo de todo el rango de temperatura de unión de funcionamiento (TJ) de -40° C a +105° C. Las especificaciones típicas representan el rendimiento a TJ = 50 ° C (TA = 25 ° C).

Cuadro 5.

| Parámetros                                                                                                                                                                                                                                             | Mínimo               | Tipo de                                | Max              | Unidad              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|------------------|---------------------|

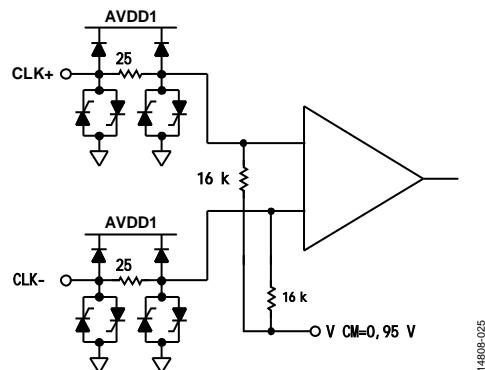

| Entrada de reloj (CLK+, CLK-) Compliance lógica Tensión de entrada diferencial Entrada Tensión de modo común Resistencia de entrada (diferencial) Capacitancia de entrada                                                                              | 600                  | LVDS/LVPECL<br>800<br>0.69 32          | 1600<br>0.9      | mV p-p V<br>K<br>pF |

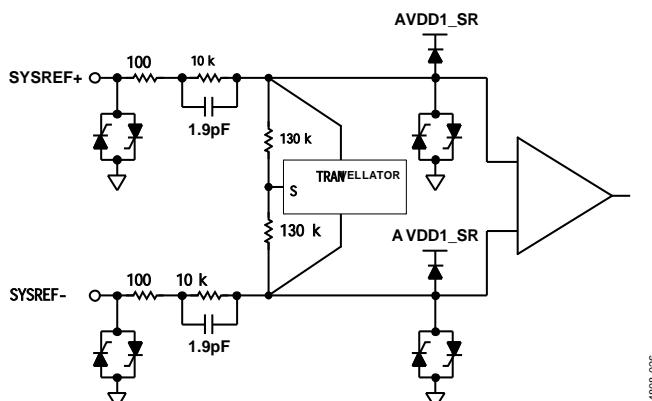

| Referencia del sistema (SYSREF) Entradas (SYSREF+, SYSREF-) 1<br>Conformidad lógica Tensión de entrada diferencial Entrada Tensión de modo común Resistencia de entrada (diferencial)<br>Capacitancia de entrada (un solo extremo por pin)             | 400<br>0.6<br>18     | LVDS/LVPECL<br>800<br>0.69<br>0.7      | 1800<br>2.2 22   | mV p-p V<br>K<br>pF |

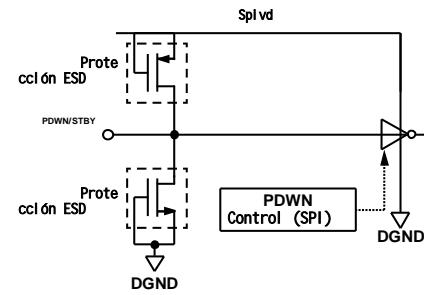

| Entrada lógica (PDWN/STBY)<br>La lógica se ajusta a la lógica 1 voltaje<br>Resistencia de entrada de voltaje lógica 0                                                                                                                                  | 0.65 × SPIVDD 0      | CMOS                                   | 0.35 × SPIVDD 10 | V<br>V M            |

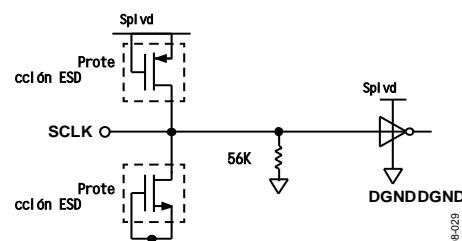

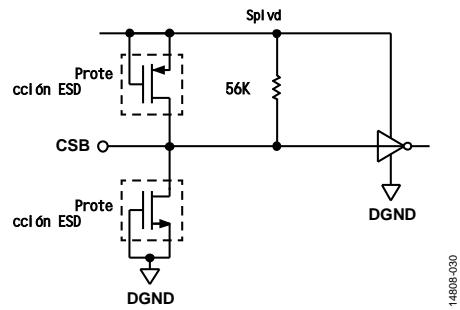

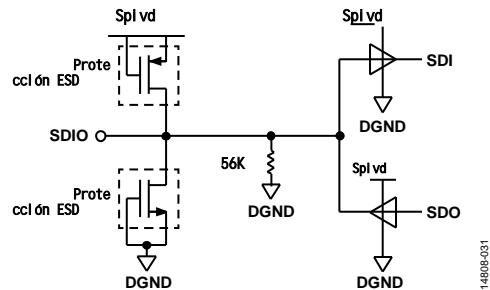

| Entradas lógicas (SDIO, SCLK, CSB)<br>La lógica se ajusta a la lógica 1 voltaje<br>Resistencia de entrada de voltaje lógica 0                                                                                                                          | 0.65 × SPIVDD 0      | CMOS                                   | 0.35 × SPIVDD 56 | V<br>V k            |

| Salida lógica (SDIO) Cumplimiento lógico<br>Voltaje lógico 1 (IOL = 800 μA) Voltaje lógico 0 (IOL = 50 μA)                                                                                                                                             | SPIVDD – 0.45 V<br>0 | CMOS                                   | 0.45             | V<br>V              |

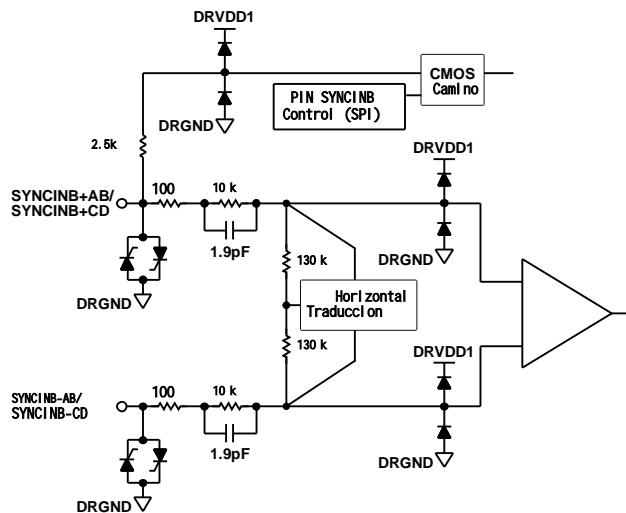

| Entrada SYNCIN (SYNCINB+AB/ SYNCINB-AB/<br>SYNCINB CD/ SYNCINB-CD) Conformidad lógica Tensión de<br>entrada diferencial Entrada Tensión de modo común Resis-<br>istencia de entrada (diferencial)<br>Capacitancia de entrada (un solo extremo por pin) | 400<br>0.6<br>18     | LVDS/LVPECL/CMOS<br>800<br>0.69<br>0.7 | 1800<br>2.2 22   | mV p-p V<br>K<br>pF |

| Salidas lógicas (FD_A, FD_B, FD_C, FD_D)<br>La lógica se ajusta a la lógica 1 voltaje<br>Resistencia de entrada de voltaje lógica 0                                                                                                                    | 0.8 × SPIVDD 0       | CMOS                                   | 0.5<br>56        | V<br>V k            |

| Salida digital (SERDOUTABx ± /SERDOUTCDx ±, x = 0 o 1)<br>Conformidad lógica<br>Tensión de salida diferencial Corriente de cortocircuito<br>(ID corto) Impedancia de terminación diferencial                                                           |                      | LMC<br>455.8<br>15<br>100              |                  | mV p-p<br>Caballo   |

1 Solo entrada de acoplamiento DC.

## ESPECIFICACIONES DEL

AVDD1 = 0,975 V, AVDD1\_SR = 0,975 V, AVDD2 = 1,8 V, AVDD3 = 2,5 V, DVDD = 0,975 V, DRVDD1 = 0,975 V, DRVDD2 = 1,8 V, SPIVDD = 1,8 V, 500 MSPS, divisor de reloj = 4, entrada diferencial a escala completa de 1,80 V p-p, referencia interna de 0,5 V, AIN = 1,0 dBFS, ajuste SPI predeterminado, a menos que se indique lo contrario. Las especificaciones mínimas y máximas están garantizadas a lo largo de todo el rango de temperatura de unión de funcionamiento (TJ) de -40° C a +105° C. Las especificaciones típicas representan el rendimiento a TJ = 50 ° C (TA = 25 ° C).

Cuadro 6.

| Parámetros                                                        | Mínimo | Tipo de | Max | Unidad                     |

|-------------------------------------------------------------------|--------|---------|-----|----------------------------|

| Reloj                                                             |        |         |     |                            |

| Velocidad de reloj (en CLK+/CLK-pin)                              | 0.3    |         | 2.4 | GHz                        |

| Tasa máxima de muestreo 1                                         | 600    |         |     | El MSPS                    |

| Frecuencia de muestreo mínima 2                                   | 240    |         |     | El MSPS                    |

| Alto ancho de pulso de reloj                                      | 125    |         |     | ps                         |

| Bajo ancho de pulso de reloj                                      | 125    |         |     | ps                         |

| Output                                                            |        |         |     |                            |

| Intervalo de unidad (UI) 3                                        | 66.67  | 100     | 593 | ps                         |

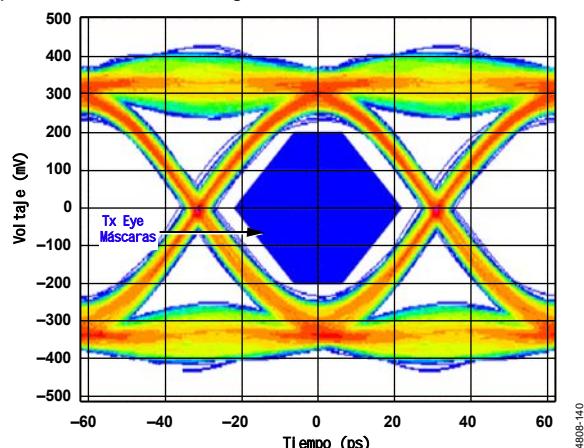

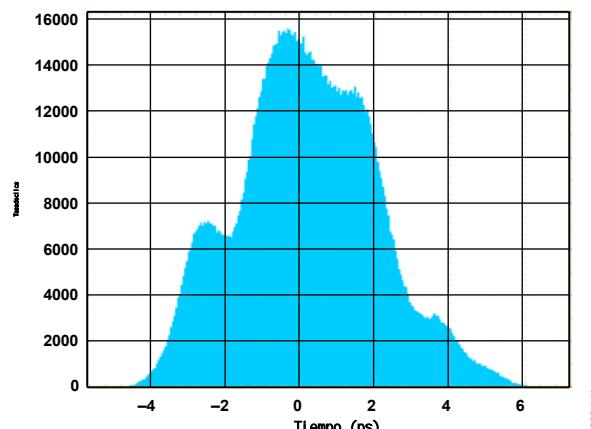

| Tiempo de ascenso (tR) (entre el 20 y el 80% de la carga de 100 ) |        | 31.25   |     | ps                         |

| Tiempo de caída (tF) (20% a 80% en una carga de 100 )             |        | 31.37   |     | ps                         |

| Tiempo de bloqueo PLL                                             |        | 5       |     | ms                         |

| Tasa de datos por canal (no retorno a cero (NRZ)) 4               | 1.6875 | 10      | 15  | Gbps                       |

| Retraso 5                                                         |        |         |     |                            |

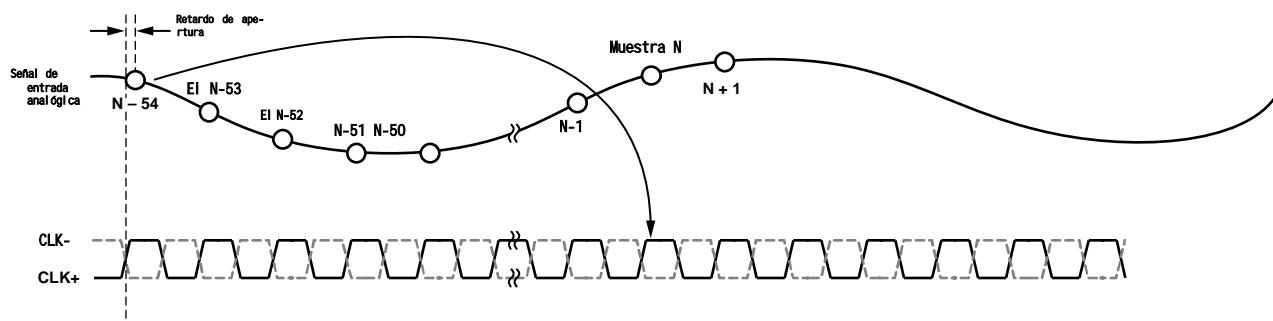

| Retraso de la tubería Retraso de detección rápido                 |        | 54      | 30  | Ciclo de reloj de muestreo |

| Ciclo de reloj de muestreo                                        |        |         |     |                            |

| Tiempo de despertar desde el modo de espera hasta el apagado      |        | 3       |     | ms                         |

|                                                                   |        | 10      |     | ms                         |

| Apertura                                                          |        |         |     |                            |

| Retardo de apertura (tA)                                          |        | 160     |     | ps                         |

| Incertidumbre de apertura (jitter, tj)                            |        | 44      |     | fs rms                     |

| Tiempo de recuperación fuera del rango                            |        | 1       |     | Ciclo de reloj de muestreo |

<sup>1</sup> La frecuencia de muestreo máxima es la frecuencia de reloj después del divisor de frecuencia.

<sup>2</sup> En el caso de L=2 o L=1, la frecuencia de muestreo mínima funciona a 240 MSPS. Véase el registro SPI 0x011A para reducir el umbral del circuito de detección de reloj.

<sup>3</sup> Velocidad de transmisión = 1/UI. Se puede soportar un subconjunto de este rango.

<sup>4</sup> El valor predeterminado para cada enlace es L=2. Este número puede variar dependiendo de la velocidad de muestreo y de la relación de decimación.

<sup>5</sup> No se usa DDC. Para cada enlace, L=2, M=2, F=2.

## Especificaciones de temporización

Cuadro 7.

| Parámetros                                              | CONDICIONES DE PRUEBA/COMENTARIOS                                                                                                     | Mínimo | Tipo de | Max  | Unidad |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------|--------|

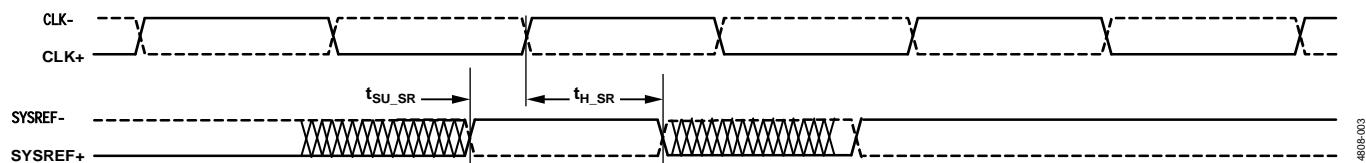

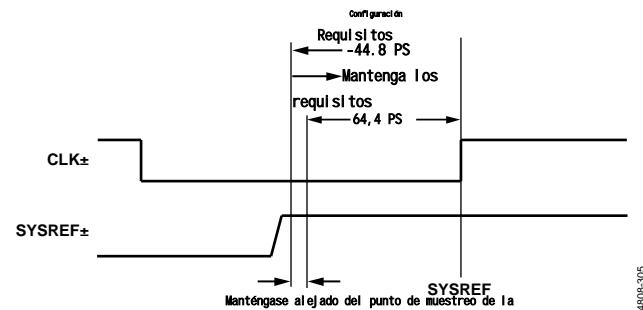

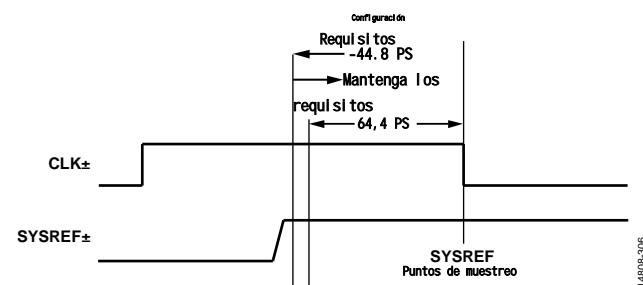

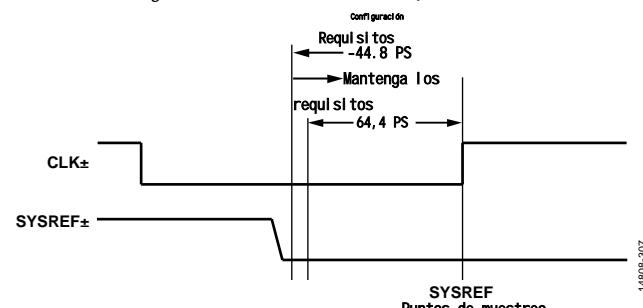

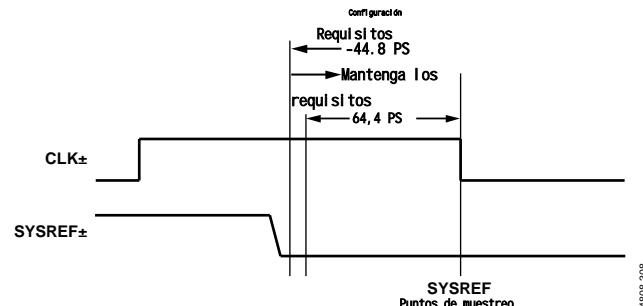

| CLK+ a SYSREF+ Requisitos de temporización $t_{SU\_SR}$ | Véase el gráfico 3<br>Reloj del dispositivo a SYSREF+ Configurar el tiempo Reloj del dispositivo a SYSREF+ Hold Time                  | -44.8  | ps      | 64.4 | ps     |

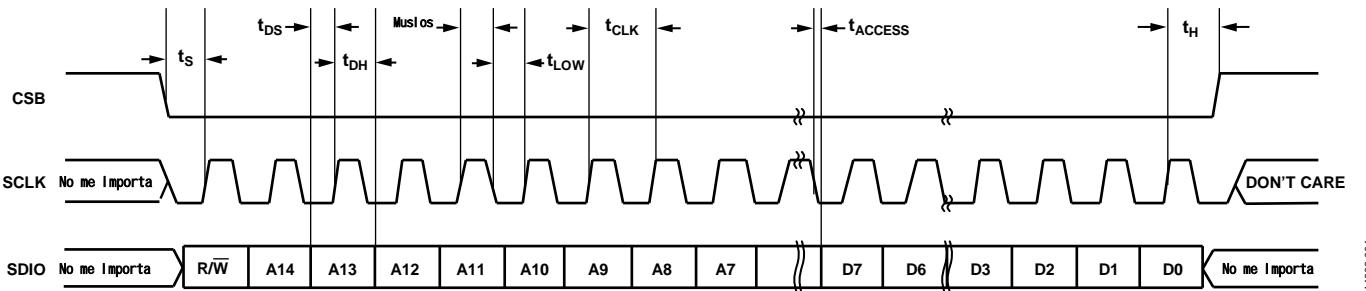

| REQUISITOS DE ESPITIMIENTO                              | Véase el gráfico 4                                                                                                                    |        |         |      |        |

| $t_{DS}$                                                | Tiempo de establecimiento entre los datos y el borde ascendente de SCLK                                                               | 4      | ns      |      |        |

| $t_{DH}$                                                | Tiempo de retención entre los datos y el borde ascendente de SCLK                                                                     | 2      | ns      |      |        |

| $t_{CLK}$                                               | El ciclo del SCLK                                                                                                                     | 40     | ns      |      |        |

| $t_s$                                                   | Tiempo de establecimiento entre el CSB y el SCLK                                                                                      | 2      | ns      |      |        |

| $t_H$                                                   | Tiempo de retención entre CSB y SCLK                                                                                                  | 2      | ns      |      |        |

| Muños                                                   | Período mínimo durante el cual SCLK debe estar en un estado lógico alto                                                               | 10     | ns      |      |        |

| Tello                                                   | SCLK debe estar en estado lógico bajo Período mínimo                                                                                  | 10     | ns      |      |        |

| $t_{ACCESS}$                                            | Retraso de tiempo máximo entre el borde descendente de SCLK y los datos de salida válidos para la operación de lectura                | 6      | ns      | 10   | ns     |

| $t_{DIS\_SDIO}$                                         | Tiempo necesario para que el pin SDIO cambie de salida a entrada con respecto al borde ascendente de CSB (no mostrado en la Figura 4) | 10     | ns      |      |        |

Diagrama de temporización

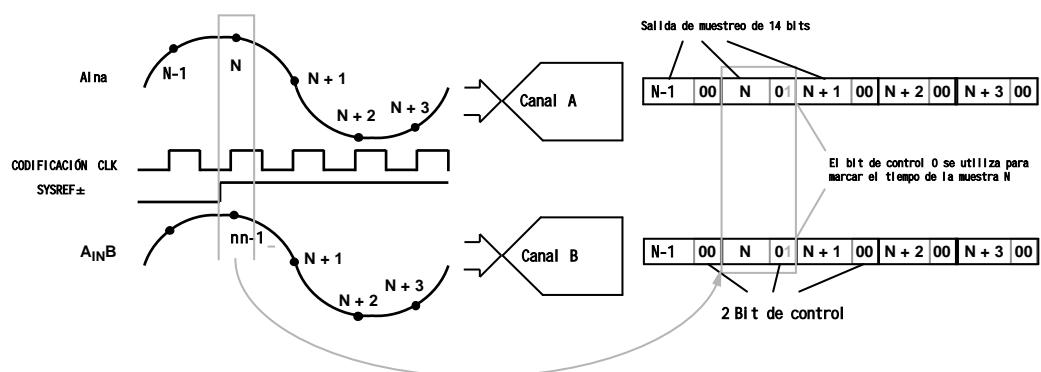

Figura 2. Tiempo de salida de datos (modo de ancho de banda completo:  $L=4$ ,  $M=2$ ,  $F=1$ )

14808-002

14808-003

Figura 3. SYSREF ± Ajuste y mantenga la temporización

Figura 4. Diagrama de temporización de la interfaz serie

14808-004

## Calificación máxima absoluta

Cuadro 8.

| Parámetros                                                                                                              | Calificación       |

|-------------------------------------------------------------------------------------------------------------------------|--------------------|

| Eléctrico                                                                                                               |                    |

| AVDD1 a AGND AVDD1_SR a AGND AVDD2 a AGND                                                                               | 1.05 V             |

| AVDD3 a AGND DVDD a DGND DRVDD1 a DGND DRVDD2 a DRGND SPIVDD a AGND VIN $\pm$ x a AGND CLK $\pm$ a AGND                 | 2.00 V             |

| SCLK, SDIO, CSB a DGND PDWN/STBY a DGND SYSREF $\pm$ a AGND_SR SYNCINB $\pm$ AB/SYNCINB $\pm$ CD a Medio ambiente DRGND | 2.70 V             |

| Rango de temperatura de unión de trabajo                                                                                | 1.05 V             |

| Temperatura máxima de unión                                                                                             | 1.05 V             |

| Rango de temperatura de almacenamiento (temperatura ambiente)                                                           | 2.00 V             |

|                                                                                                                         | 2.00 V             |

|                                                                                                                         | 0.3V a AVDD3+0.3V  |

|                                                                                                                         | 0.3V a AVDD1+0.3V  |

|                                                                                                                         | 0.3V a SPIVDD+0.3V |

|                                                                                                                         | 0.3V a SPIVDD+0.3V |

|                                                                                                                         | 0V a 2.5V          |

|                                                                                                                         | 0V a 2.5V          |

|                                                                                                                         | 40° C a +105° C    |

|                                                                                                                         | 125°C              |

|                                                                                                                         | 65° C a +150° C    |

Alcanzar o superar las tensiones enumeradas bajo la calificación máxima absoluta puede causar daños permanentes al producto. Esto es simplemente una escalada de presión; No se implica el funcionamiento funcional del producto en estas condiciones o en cualquier otra condición que sea superior a las indicadas en la sección de funcionamiento de esta descripción. El funcionamiento por encima de las condiciones máximas de funcionamiento durante períodos prolongados puede afectar a la fiabilidad del producto.

## Resistencia térmica

El rendimiento térmico está directamente relacionado con el diseño de la placa de circuito impreso (PCB) y el entorno operativo. Se requiere una cuidadosa atención al diseño térmico de la PCB.

Ja es la unión de convección natural con la resistencia térmica ambiental medida en una carcasa sellada de un pie cúbico. Jc\_bot es la unión inferior con la resistencia térmica de la carcasa.

## Cuadro 9. Resistencia térmica

| Tipo de PCB         | Velocidad del flujo de aire (m/s) | Ja                   | Jc_bot              | Unidad |

|---------------------|-----------------------------------|----------------------|---------------------|--------|

| Jedec               | 0.0                               | 21.58 <sup>1,2</sup> | 1.95 <sup>1,4</sup> | °C/W   |

| Placa 2s2p          | 1.0                               | 17.94 <sup>1,2</sup> | N/A <sup>3</sup>    | °C/W   |

| Tablero de 10 capas | 2.5                               | 16.58 <sup>1,2</sup> | N/A <sup>3</sup>    | °C/W   |

<sup>1</sup> Segundo JEDEC 51-7, más una placa de prueba JEDEC 51-5 2s2p.

<sup>2</sup> Segundo JEDEC JESD51-2 (aire estacionario) o JEDEC JESD51-6 (aire móvil). <sup>3</sup> N/A significa que no se aplica.

<sup>4</sup> De acuerdo con MIL-STD 883, Método 1012.1.

## ADVERTENCIA ESD

### ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

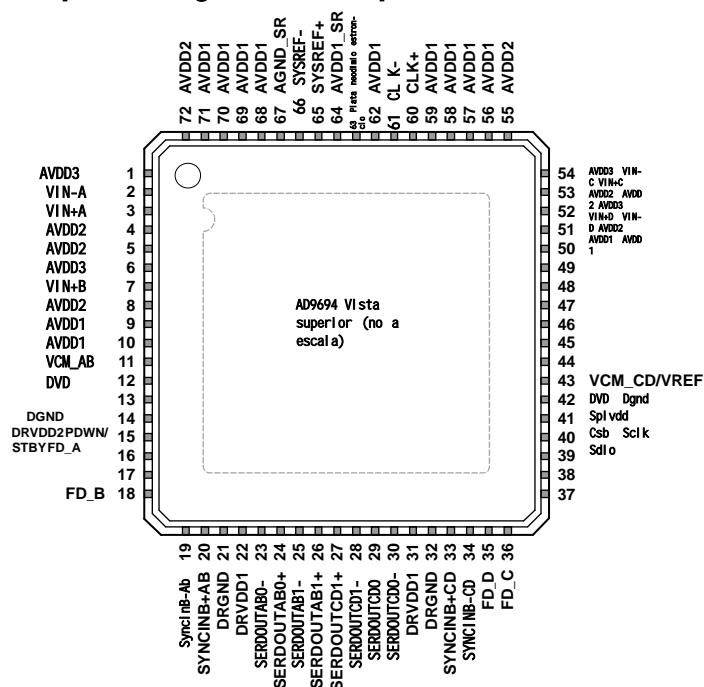

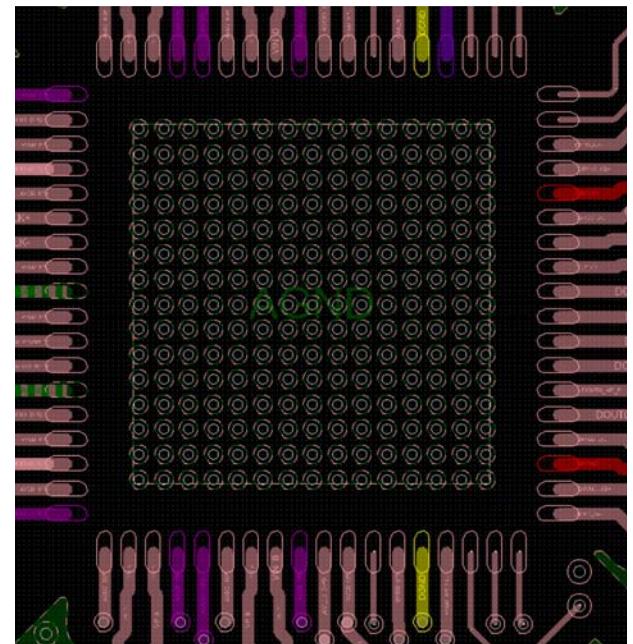

## Configuración de pines y descripción de la función

## Notas

1. Almohadillas expuestas. Conexión a tierra analógica. Las almohadillas térmicas expuestas en la parte inferior del paquete proporcionan una referencia a tierra para AVDDx, SPIVDD, DVDD, DRVDD1 y DRVDD2.

Esta almohadilla expuesta debe estar conectada a tierra para funcionar correctamente.

4808-005

Figura 5. CONFIGURACIÓN DE PINES (vista superior)

Cuadro 10. Descripción de la función del pin

| Pin No.                                            | Mnemonic               | Tipo de    | Descripción                                                                                                                                                                                                                                                                              |

|----------------------------------------------------|------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                  | AGND/EPAD              | Terreno    | Almohadillas expuestas. Conexión a tierra analógica. Almohadillas térmicas expuestas. La parte inferior del paquete proporciona una referencia a tierra para AVDDx, SPIVDD, DVDD, DRVDD1 y DRVDD2. Esta almohadilla expuesta debe estar conectada a tierra para funcionar correctamente. |

| 1, 6, 49, 54                                       | AVDD3                  | Suministro | Fuente de alimentación analógica (2,5 V nominal).                                                                                                                                                                                                                                        |

| 2, 3                                               | VIN-A, VIN+A           | Entrar     | Complemento de entrada analógica ADC/verdadero.                                                                                                                                                                                                                                          |

| 4, 5, 9, 46, 50, 51, 55, 72                        | AVDD2                  | Suministro | Fuente de alimentación analógica (nominal 1,8 V).                                                                                                                                                                                                                                        |

| 7, 8                                               | VIN+B, VIN-B           | Entrar     | ADC B Entrada analógica Verdadero/Complemento.                                                                                                                                                                                                                                           |

| 10, 11, 44, 45, 56, 57, 58, 59, 62, 68, 69, 70, 71 | AVDD1                  | Suministro | Fuente de alimentación analógica (0,975 V nominal).                                                                                                                                                                                                                                      |

| 12                                                 | VCM_AB                 | Output     | Una salida polarizada a nivel de modo común para el canal de entrada analógica A y el canal B.                                                                                                                                                                                           |

| 13, 42                                             | DVD                    | Suministro | Fuente de alimentación digital (0,975 V nominal).                                                                                                                                                                                                                                        |

| 14, 41                                             | DGND                   | Terreno    | Referencia de tierra para DVDD y SPIVDD.                                                                                                                                                                                                                                                 |

| 15                                                 | DRVDD2                 | Suministro | Fuente de alimentación digital (nominal 1.8V) para JESD204B PLL.                                                                                                                                                                                                                         |

| 16                                                 | PDWN/STBY              | Entrar     | Entrada de apagado/en espera (alto activo). El funcionamiento de este pin depende del modo SPI y se puede configurar para ser apagado o en espera. Este pin requiere una resistencia pull-down externa de 10 k.                                                                          |

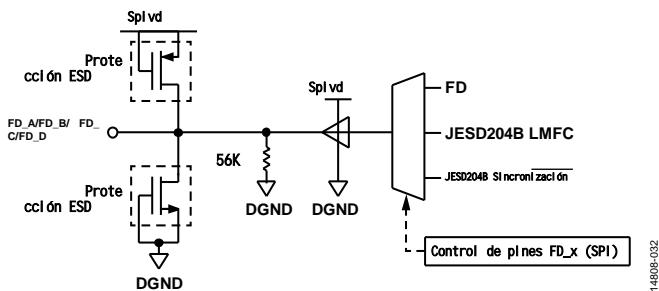

| 17, 18, 35, 36                                     | FD_A, FD_B, FD_D, FD_C | Output     | Detección rápida de las salidas del canal A, canal B, canal C y canal D.                                                                                                                                                                                                                 |

| 19                                                 | SYNCINB-AB             | Entrar     | Complemento de entrada de sincronización de LVDS JESD204B bajo efectivo para el canal A y el canal B.                                                                                                                                                                                    |

| 20                                                 | SYNCINB+AB             | Entrar     | Las entradas de sincronización LVDS/CMOS JESD204B bajas efectivas para los canales A y B son verdaderas.                                                                                                                                                                                 |

| Pin No. | Mnemonic                  | Tipo de            | Descripción                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21, 32  | DRGND                     | Terreno            | Referencia a tierra para DRVDD1 y DRVDD2.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22, 31  | DRVDD1                    | Suministro         | Fuente de alimentación digital (nominal 0.975 V) para pines SERDOUTABx $\pm$ /SERDOUTCDx $\pm$ .                                                                                                                                                                                                                                                                                                                                                                         |

| 23, 24  | Serdoutab 0 , SERDOUTAB0+ | Output             | El canal 0 emite el complemento/verdadero de datos para el canal A y el canal B.                                                                                                                                                                                                                                                                                                                                                                                         |

| 25, 26  | Serdoutab 1 , SERDOUTAB1+ | Output             | El canal 1 da salida a los datos supplementarios/verdadero para el canal A y el canal B.                                                                                                                                                                                                                                                                                                                                                                                 |

| 27, 28  | SERDOUTCD1+, Serdoutcd 1  | Output             | El canal 1 da salida a los datos de verdadero/complemento del canal C y del canal D.                                                                                                                                                                                                                                                                                                                                                                                     |

| 29, 30  | SERDOUTCD0+, Serdoutcd 0  | Output             | El canal 0 da salida a los datos de verdadero/complemento del canal C y del canal D.                                                                                                                                                                                                                                                                                                                                                                                     |

| 33      | SYNCINB+CD                | Entrar             | Las entradas de sincronización LVDS/CMOS/LVPECL JESD204B bajas válidas para el canal C y el canal D son verdaderas.                                                                                                                                                                                                                                                                                                                                                      |

| 34      | SYNCINB-CD                | Entrar             | Complemento de entrada de sincronización LVDS/CMOS/LVPECL JESD204B efectivo bajo para el canal C y el canal D.                                                                                                                                                                                                                                                                                                                                                           |

| 37      | SDIOSCLKCSBSPIVDD         | Entrada/           | Entrada/salida de datos en serie SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

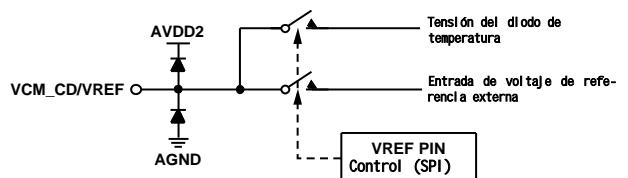

| 38      | VCM_CD/VREF               | salida Entrada     | Reloj serie SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

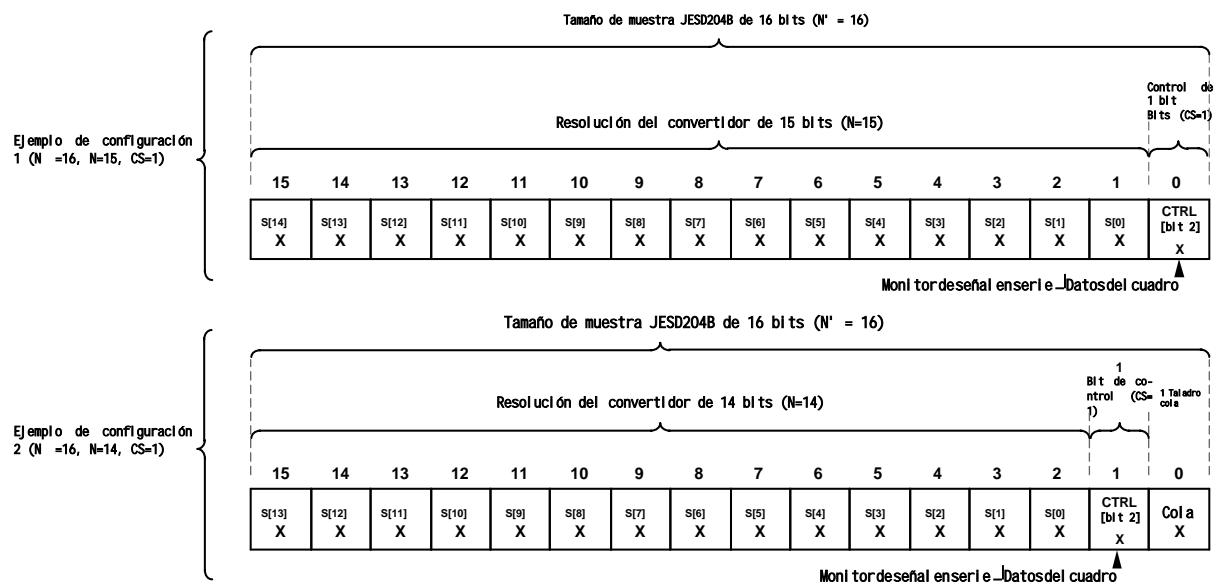

| 39      |                           |                    | Selección de chip SPI (bajo activo).                                                                                                                                                                                                                                                                                                                                                                                                                                     |