## ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

要約 ; 要約 ; 要約

通信、グラフィック、イメージングアプリケーション

向けの高性能信号処理装置

スーパーハーバードアーキテクチャ

デュアルデータフェッチ、命令フェッチ、非侵入I/Oのための4つの独立したバス

32ビットIEEE浮動小数点計算ユニット-乗算器、ALU、およびシフタ

デュアルポートされたオンチップスラムと統合されたI/O周辺機器-完全なチップ上のシステム

統合されたマルチ処理機能

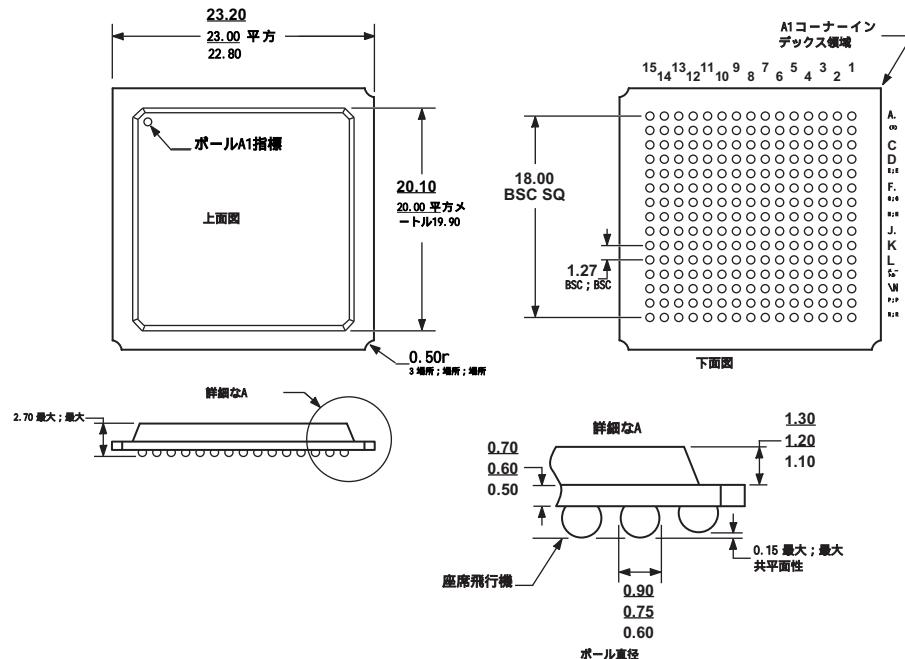

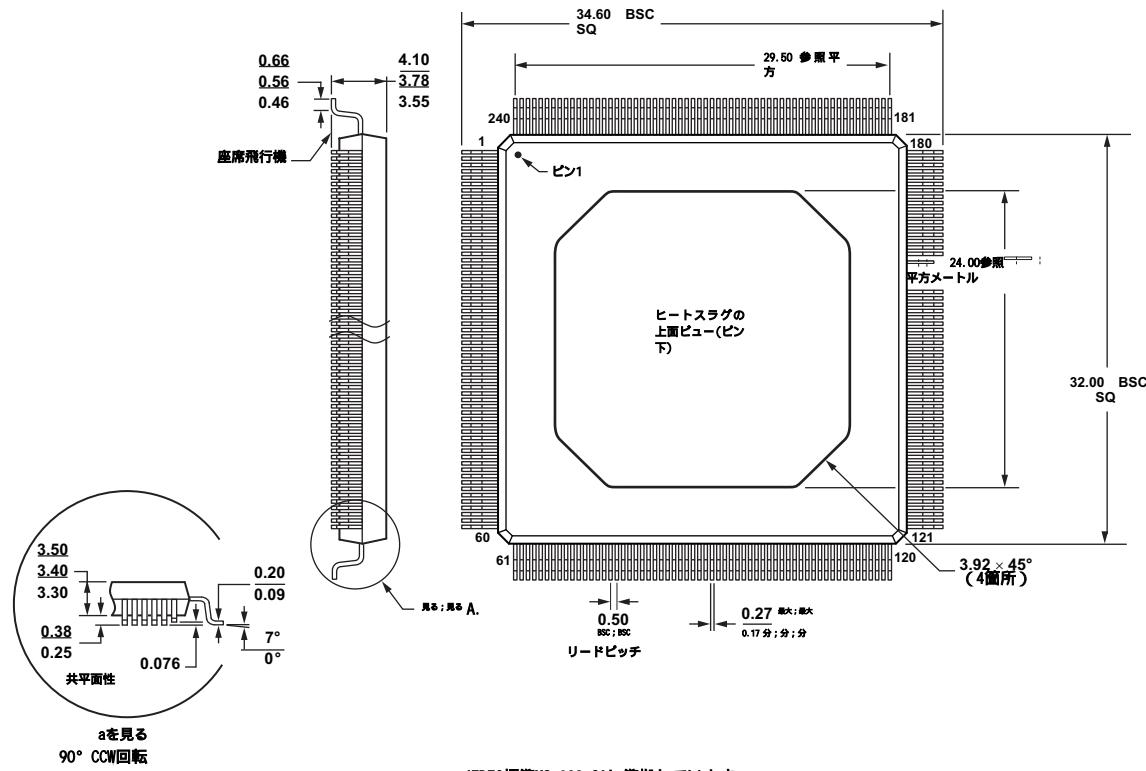

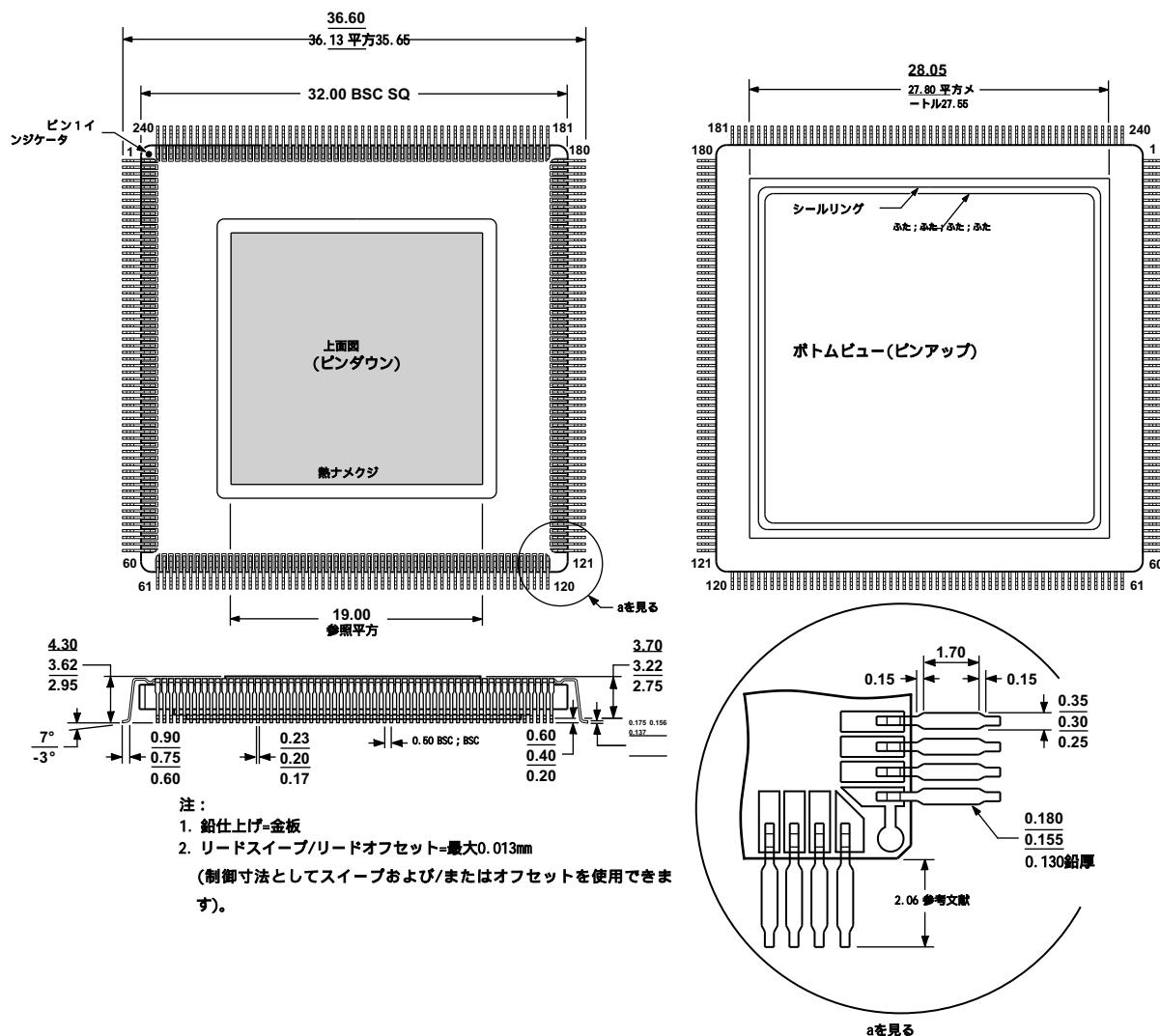

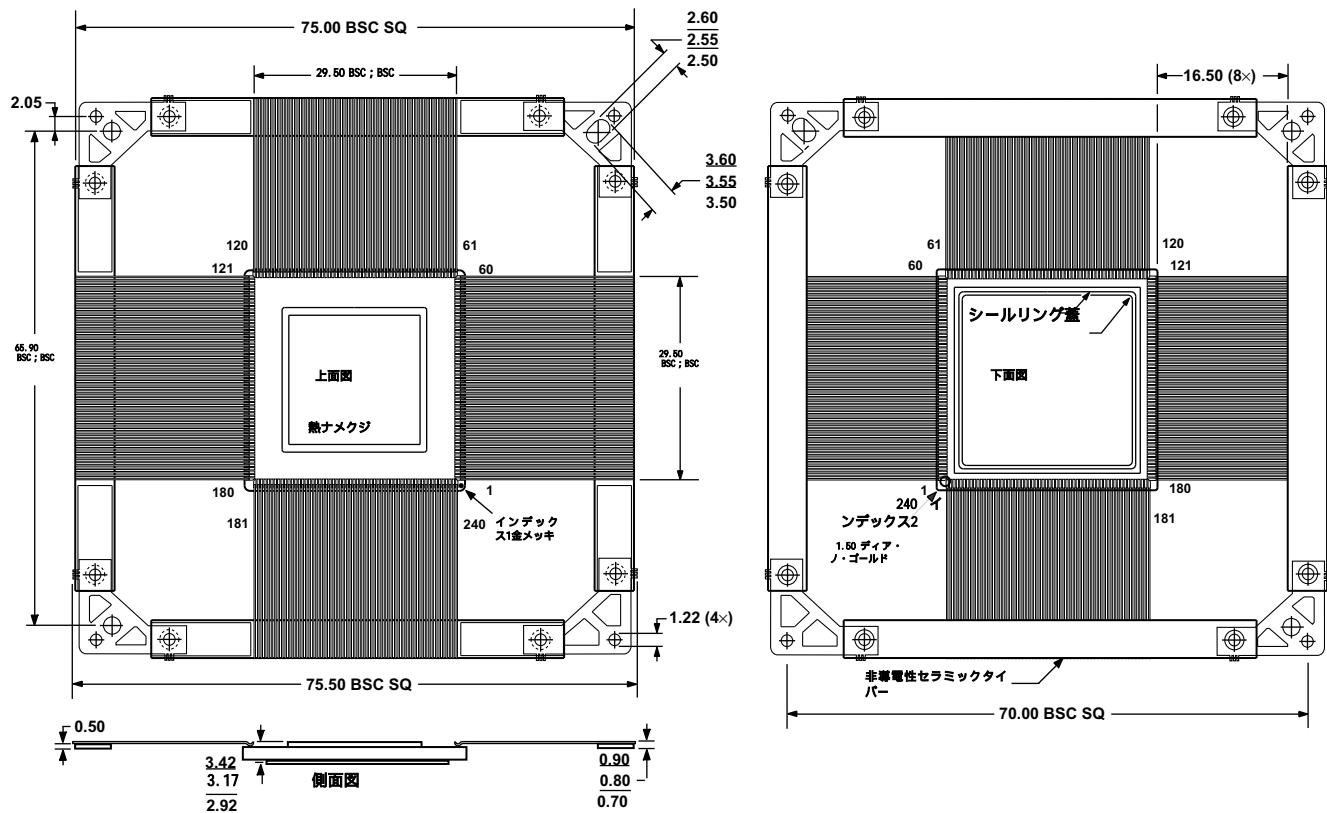

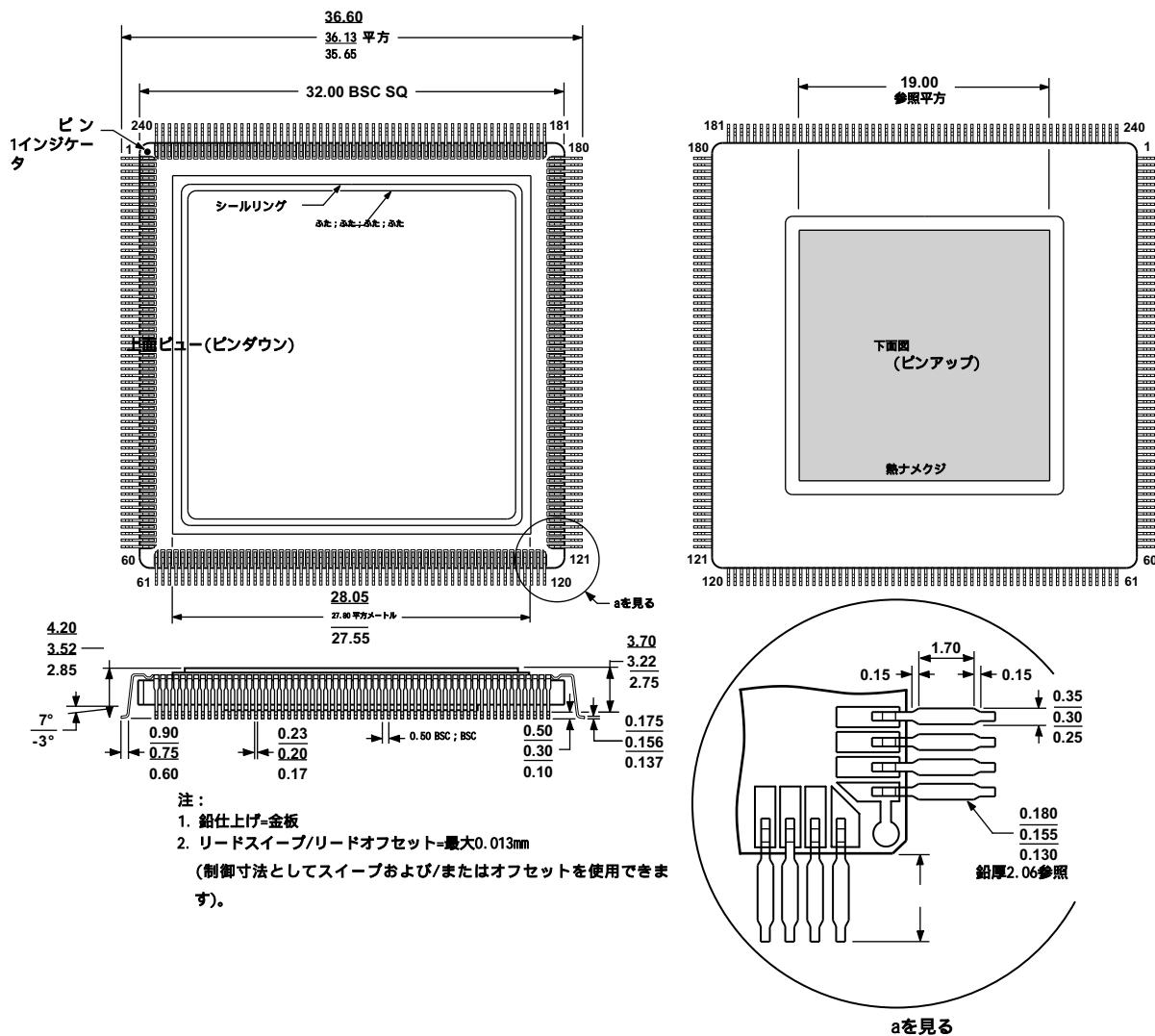

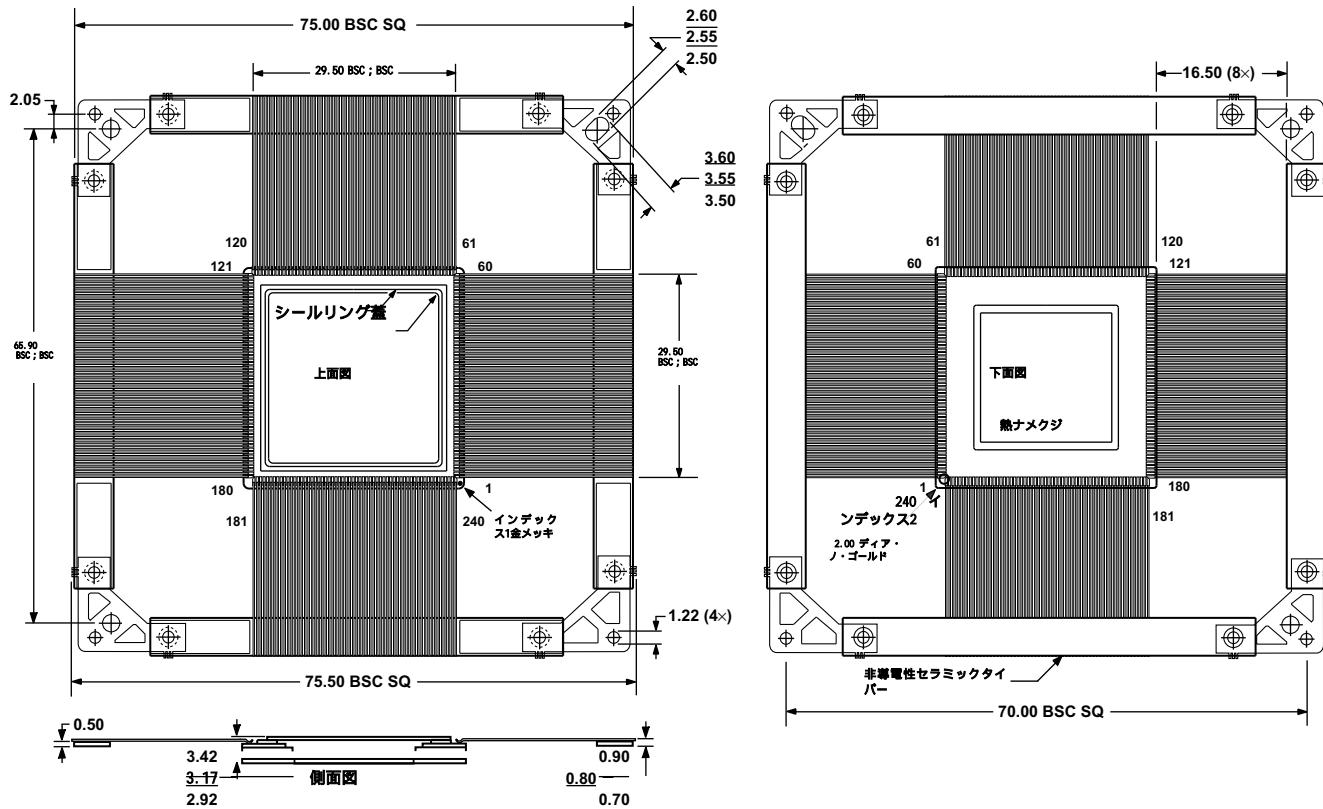

240リード熱強化MQFP\_PQ4パッケージ、225ポールプラスチックポールグリッドアレイ(PBGA)、240リード密閉CQFP

パッケージ

RoHS準拠パッケージ

主な機能-プロセッサーコア

40 MIPS、25 ns命令率、シングルサイクル命令実行

120 MFLOPSピーク、80 MFLOPS持続パフォーマンスデュアルデータアドレスジェネレータ、モジュロおよびピットリバースアドレス指定)

ゼロオーバーヘッドラープによる効率的なプログラムシーケンシング：シングルサイクルループセットアップ

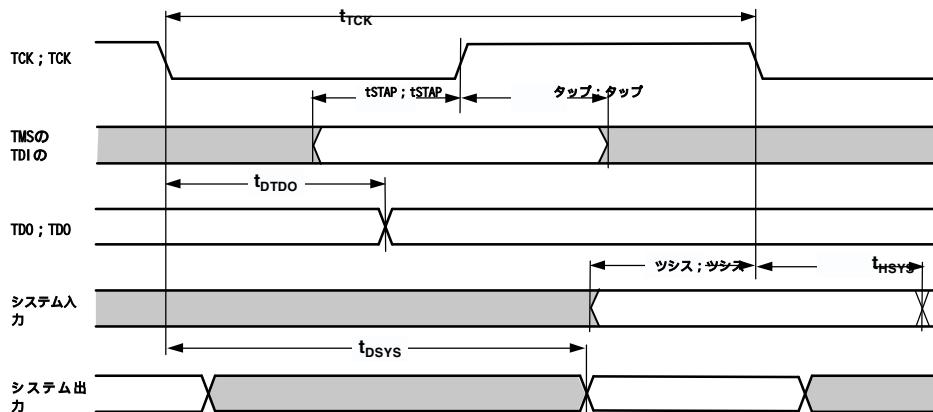

IEEE JTAG標準1149.1テストアクセスポートとオンチップエミュレーション

32ビット単一精度および40ビット拡張精度IEEE浮動小数点データフォーマットまたは32ビット固定小数点データフォーマット

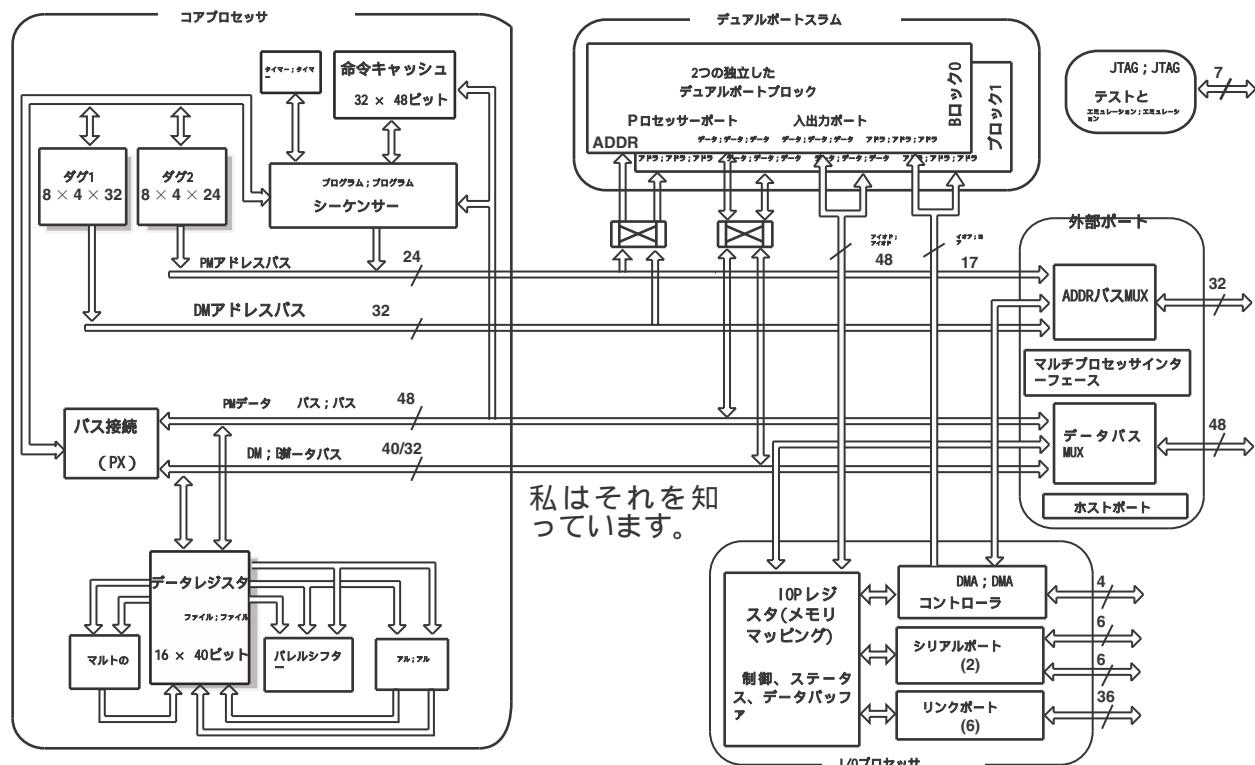

図1. 機能ブロック図

SHARCおよびSHARCロゴは、アナログデバイス、株式会社の登録商標です。

回転H

文書フィードバック

アナログデバイスによって提供される情報は正確で信頼性があると考えられています。ただし、アナログデバイスは、その使用、またはその使用に起因する第三者の特許またはその他の権利の侵害について一切の責任を負いません。仕様は予告なく変更される場合があります。アナログデバイスの特許または特許権に基づいて、暗黙的またはその他の方法でライセンスは付与されません。商標および登録商標は、それぞれの所有者の財産です。

ワントクノロジーウェイ、P.O.ボックス9106、ノーウッド、MA 02062-9106 U.S.A.電話 : 781.329.4700 ©2013アナログデバイス株式会社すべての権利は所有されます。

技術的サポート

[www.analog.com](http://www.analog.com)

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 並列計算

デュアルメモリの読み取り/書き込みおよび命令フェッチと並行したシングルサイクル乗算およびALU操作

加速されたFFTパタフライ計算のための加算と減算を掛け

る

## 最大4MビットのオンチップSRAM

コアプロセッサとDMAによる独立したアクセスのためのデュアルポート

## オフチップメモリインタフェース

アドレス指定可能な4ギガワード

プログラム可能な待機状態生成、ページモードDRAM

サポート

## DMAコントローラ

10 ADSP-2106x内部メモリと外部メモリ、外部周辺機器、ホストプロセッサ、シリアルポート、またはリンクポート

間の転送用のDMAチャネル

フルスピードプロセッサの実行と並行して、最大40 MHzの

バックグラウンドDMA転送

## 16ビットおよび32ビットマイクロプロセッサへのホストプロセッサインタフェース

ホストはADSP-2106x内部メモリとIOPレジスタを直接読み取り/書き込むことができます

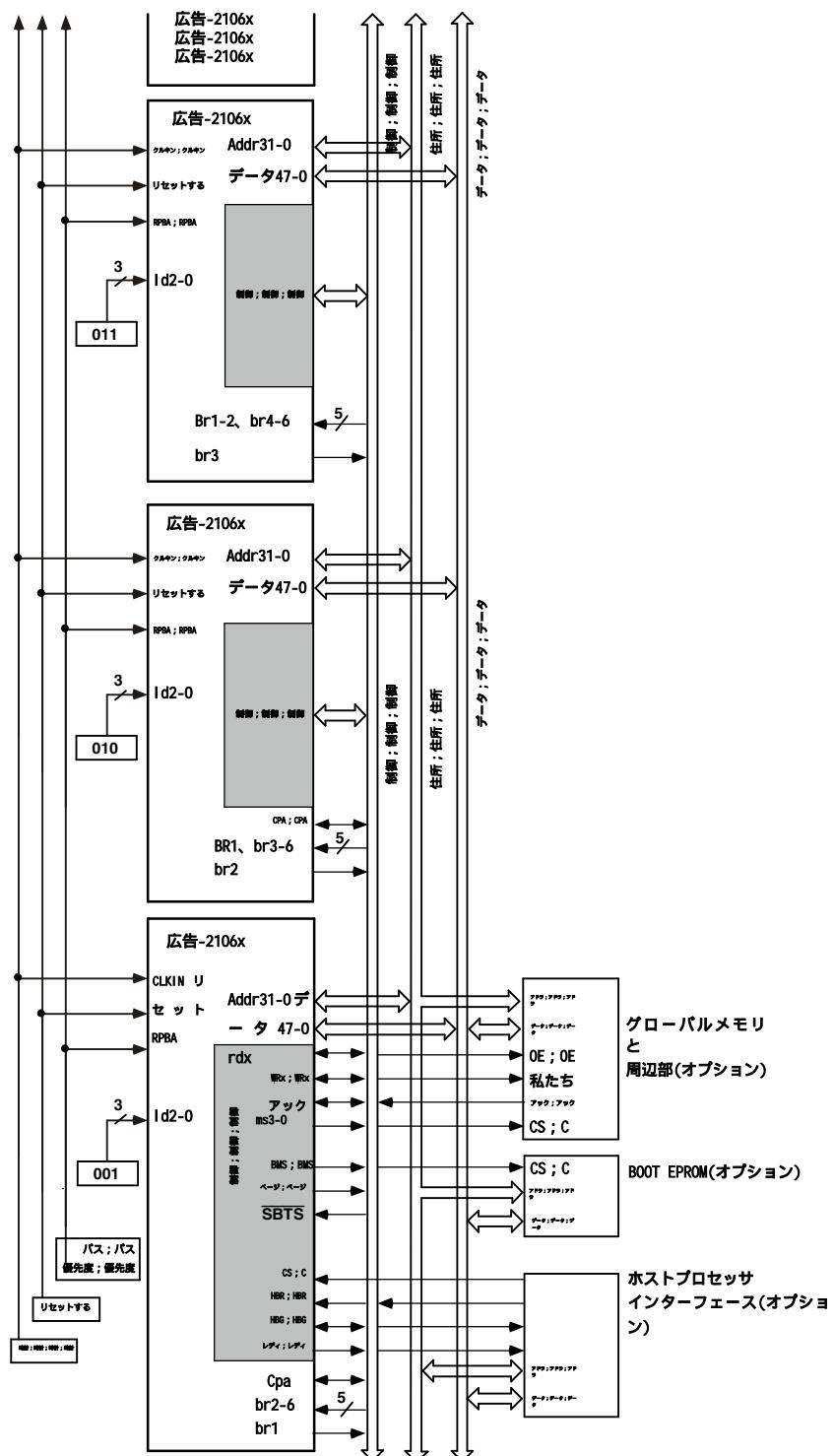

## 多重処理

スケーラブルなDSPマルチプロセッションアーキテクチャのための接着レス接続

最大6つのADSP-2106xsプラスホストの並列バス接続用の分散オンチップバス調停

ポイントツーポイント接続とアレイマルチ処理用の6つのリンクポート

240 バラレルバス経由のMbps転送レート

240 リンクポートを介したMbps転送レート

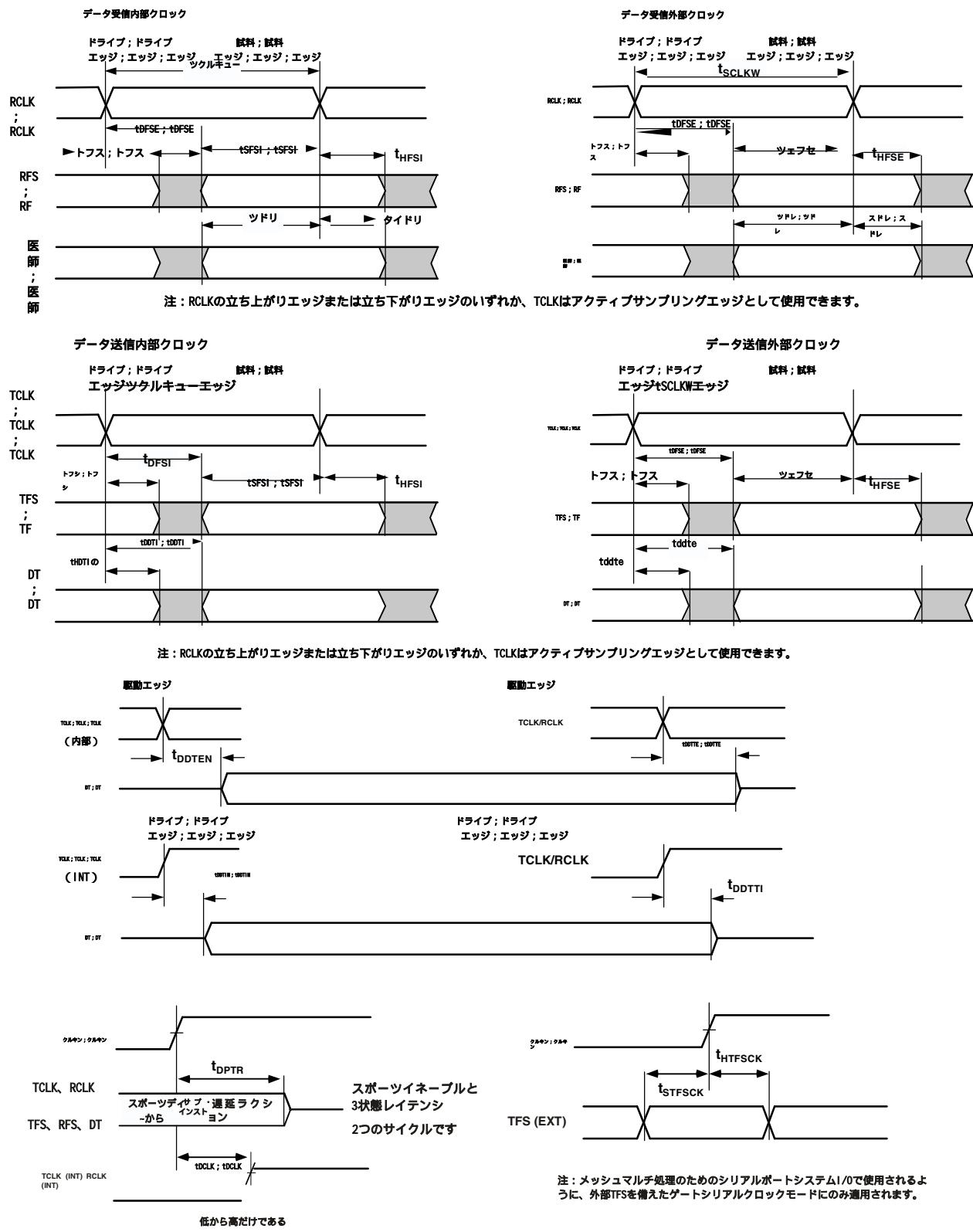

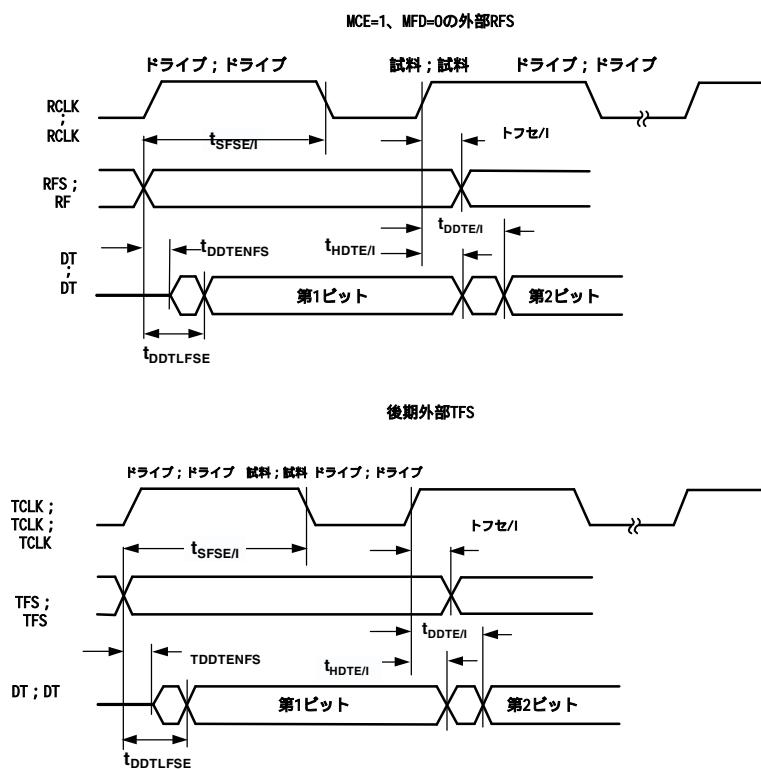

## シリアルポート

コンパニーディングハードウェアを備えた2つの40 Mbps同期シリアルポート

独立した送受信機能

表1。ADSP-2106x SHARCプロセッサーファミリーの機能

| 特徴          | 広告-21060           | 広告-21062           | 広告-21060L          | 広告-21062L          | 広告-21060C          | ADSP-21060LC       |

|-------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| スラム；スラム；スラム | 4Mビット              | 2Mビット              | 4Mビット              | 2Mビット              | 4Mビット              | 4Mビット              |

| 動作電圧        | 5 V.               | 5 V.               | 3.3 V.             | 3.3 V.             | 5 V.               | 3.3 V.             |

| 命令レート       | 33 MHzの<br>40 MHzの |

| パッケージ       | MQFP_PQ4PBGA       | MQFP_PQ4PBGA       | MQFP_PQ4PBGA       | MQFP_PQ4PBGA       | CQFP               | CQFP               |

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 内容；内容

|                                 |    |

|---------------------------------|----|

| まとめ .....                       | 1  |

| 一般的な説明 .....                    | 4  |

| SHARCファミリーコアアーキテクチャ .....       | 4  |

| メモリとI/Oインターフェースの機能 .....        | 5  |

| 開発ツール .....                     | 8  |

| 追加情報 .....                      | 9  |

| 関連信号鎖 .....                     | 9  |

| ピン機能の説明 .....                   | 10 |

| EZ-ICEプローブ用ターゲットボードコネクタ .....   | 13 |

| ADSP-21060/ADSP-21062仕様 .....   | 15 |

| 運転条件 (5v) .....                 | 15 |

| 電気特性(5v) .....                  | 15 |

| 内部消費電力 (5v) .....               | 16 |

| 外部消費電力 (5v) .....               | 17 |

| ADSP-21060L/ADSP-21062L仕様 ..... | 18 |

| 運転条件 (3.3v) .....               | 18 |

| 電気特性(3.3v) .....                | 18 |

| 内部消費電力 (3.3v) .....             | 19 |

| 外部消費電力 (3.3v) .....             | 20 |

| 絶対最大評価 .....                    | 20 |

| ESDの注意 .....                    | 21 |

| パッケージマーキング情報 .....              | 21 |

| タイミング仕様 .....                   | 21 |

| 試験条件 .....                      | 48 |

| 環境条件 .....                      | 51 |

| 225ポールPBGAポール構成 .....           | 52 |

| 240リードMQFP_PQ4/CQFPピン構成 .....   | 54 |

| 輪郭寸法 .....                      | 56 |

| 表面実装設計 .....                    | 61 |

| 注文ガイド .....                     | 62 |

## 改訂履歴

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| 3/13-rev.g to rev.h更新された開発ツール .....                                        | 8  |

| PTOTAL=PEXTから消費電力方程式を修正しました<br>(IDDIN2 × 5.0v)からPTOTAL=PEXT(IDDIN2 × 3.3v) |    |

| 外部消費電力 (3.3v) .....                                                        | 20 |

# **ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC**

## 一般的な説明

ADSP-2106x SHARC® – Super Harvard Architecture Computer – は、高いレベルのDSPパフォーマンスを提供する32ビット信号処理マイクロコンピュータです。ADSP-2106xはADSP-21000 DSPコアに基づいて完全なチップ上のシステムを形成し、デュアルポートされたオンチップSRAMと専用のI/Oバスでサポートされた統合されたI/O周辺機器を追加します。

高速で低電力のCMOSプロセスで作製されたADSP-2106xは、命令サイクル時間が25nsで、40 MIPSで動作します。プロセッサは、オンチップ命令キャッシュにより、1サイクルですべての命令を実行できます。表2は、ADSP-2106xのパフォーマンスベンチマークを示しています。

ADSP-2106x SHARCは、高性能浮動小数点DSPコアと、最大4MビットSRAMメモリ(表1を参照)、ホストプロセッサーインターフェースを含む統合されたオンチップシステム機能を組み合わせた信号コンピュータの統合の新しい標準を表します。、DMAコントローラ、シリアルポートとリンクポート、および接着剤のないDSPマルチプロセッシングのためのパラレルバス接続。

表2. ベンチマーク (40 MHz)

| ベンチマークアルゴリズム         | スピード        | サイクル   |

|----------------------|-------------|--------|

| 1024点複合FFT(基数4、反転付き) | 0.46 μs     | 18,221 |

| モミフィルター(タップごと)       | 25 ns       | 1      |

| IIRフィルター(バイクワッドごと)   | 100 ns      | 4      |

| 分割(y/x)              | 150 ns      | 6      |

| 逆平方根                 | 225 ns      | 9      |

| DMA転送速度              | 240 エムバイト/秒 |        |

ADSP-2106xは、高性能の32ビットDSPコアと統合されたオンチップシステム機能を組み合わせて、SHARCの業界トップのDSP統合基準を継続しています。ページ1のプロック図は、次のアーキテクチャ特徴を示しています。

- ? 共有データレジスタファイルを持つ計算ユニット(ALU、乗算器、シフタ)

- ? データアドレスジェネレータ(DAG1、DAG2)

- ? 命令キャッシュ付きプログラムシーケンサ

- ? コア・プロセッサのサイクルごとにメモリとコア間で4つの32ビットデータ転送をサポートするPMおよびDMバス

- ? 間隔タイマー

- ? オンチップSRAM

- ? オフチップメモリおよび周辺機器とのインターフェース用外部ポート

- ? ホストポートおよびマルチプロセッサーインターフェース

- ? DMAコントローラ

- ? シリアルポートとリンクポート

- ? JTAGテストアクセスポート

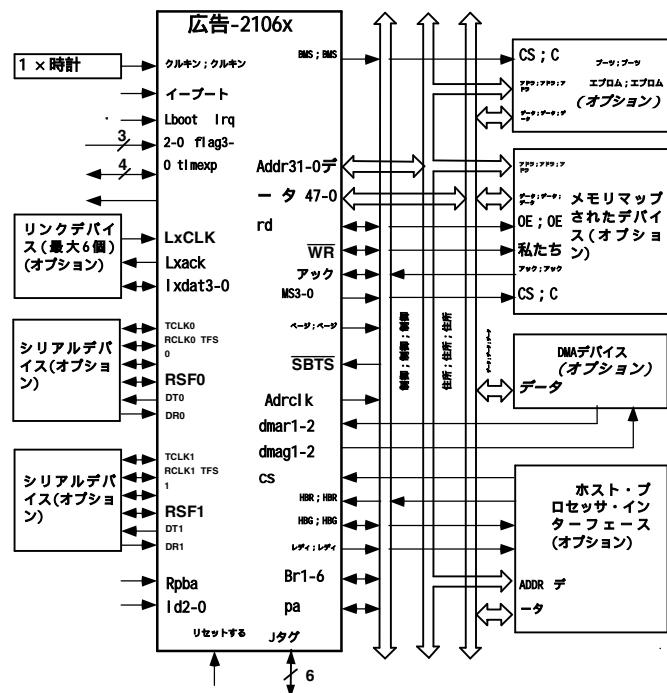

図2。ADSP-2106xシステムサンプル構成

## SHARCファミリーコアアークティクチャ

ADSP-2106xには、ADSP-21000ファミリーコアの以下のアーキテクチャ機能が含まれています。

## 独立した並列計算ユニット

演算論理ユニット（ALU）、乗算器、およびシフタは、すべて単一サイクル命令を実行します。3つのユニットは並列に配置されており、計算スループットを最大化します。単一の多関数命令は並列アルゴリズムと乗算演算を実行する。これらの計算ユニットは、IEEE 32ビット単精度浮動小数点、拡張精度40ビット浮動小数点、および32ビット固定点データ形式をサポートしています。

データレジスタファイル

前記演算部と前記データバスとの間でデータを転送し、中間結果を記憶するために汎用のデータレジスタファイルを用いる。この10ポート、32レジスタ(16プライマリ、16セカンダリ)レジスタファイルは、ADSP-21000 Harvard アーキテクチャと組み合わせることで、計算ユニットと内部メモリ間の制約のないデータフローを可能にします。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 命令と2つのオペランドの単一サイクルフェッチ

ADSP-2106xは、データメモリ(DM)バスがデータを転送し、プログラムメモリ(PM)バスが命令とデータの両方を転送する強化されたHarvardアーキテクチャを備えています(ページ1の図1を参照)。独立したプログラムとデータメモリバスとオンチップ命令キャッシュを使用すると、プロセッサは2つのオペランドと1つの命令(キャッシュから)を同時に取得でき、すべて1サイクルで取得できます。

## 命令キャッシュ

前記ADSP-2106xは、命令と2つのデータ値を取り込むための3バス動作を可能にするオンチップ命令キャッシュを備える、キャッシュは選択的です-フェッチがPMバスデータアクセスと競合する命令のみがキャッシュされます。これにより、デジタルフィルタの乗算蓄積やFFTバタフライ処理などのコア・ループ動作をフルスピードで実行できます。

## ハードウェア円形バッファ付きデータアドレスジェネレータ

ADSP-2106xの2つのデータアドレスジェネレータ(DAGs)は、ハードウェアに円形のデータバッファを実装します。円形バッファは、デジタル信号処理に必要な遅延線やその他のデータ構造の効率的なプログラミングを可能にし、デジタルフィルタやフーリエ変換で一般的に使用されます。ADSP-2106xの2つのダグには、最大32個の円形バッファ(16個のプライマリレジスタセット、16個のセカンダリレジスタセット)を作成できる十分なレジスタが含まれています。ダグはアドレスポインタのラップアラウンドを自動的に処理し、オーバーヘッドを削減し、パフォーマンスを向上させ、実装を簡素化します。円形バッファは、任意のメモリ場所で開始および終了することができます。

## 柔軟な指示セット

48ビットの命令ワードは、簡潔なプログラミングのために、さまざまな並列演算を収容します。例えば、ADSP-2106xは、乗算、加算、減算、分岐を、すべて1つの命令で条件付きで実行することができます。

## メモリとI/Oインターフェースの機能

ADSP-2106xプロセッサは、SHARCファミリーコアに次のアーキテクチャ機能を追加します。

## デュアルポート型オンチップメモリ

ADSP-21062/ADSP-21062Lは2メガビットのオンチップSRAMを含み、ADSP-21060/ADSP-21060Lは4MビットのオンチップSRAMを含んでいる。前記内部メモリは、前記ADSP-21062/ADSP-21062Lのそれぞれ1Mビットの2つの等サイズブロックと、前記ADSP-21060/ADSP-21060Lのそれぞれ2Mビットの2つの等サイズブロックとで構成される、それぞれは、コードとデータストレージのさまざまな組み合わせ用に構成できます。各メモリブロックは、コアプロセッサとI/OプロセッサまたはDMAコントローラによる单一サイクルの独立したアクセスのためにデュアルポートされています。デュアルポートされたメモリと個別のオンチップバスにより、コアからの2つのデータ転送とI/Oからの1つのデータ転送が可能になり、すべて1サイクルで行われます。ADSP-21062/ADSP-21062Lでは、メモリは、32ビットデータの最大64kワード、16ビットデータの128kワード、48ビット命令(または40ビットデータ)の40kワード、または最大2メガビットまでの異なるワードサイズの組み合わせとして構成できます。すべてのメモリは、16ビット、32ビット、または48ビットのワードとしてアクセスできます。

ADSP-21060/ADSP-21060Lでは、メモリを最大128kワードの32ビットデータ、256kwordsの16ビットデータ、80kワードの48ビット命令(または40ビットデータ)、または4メガビットまでの異なるワードサイズの組み合わせとして構成できます。すべてのメモリは、16ビット、32ビット、または48ビットのワードとしてアクセスできます。16ビット浮動小数点記憶フォーマットをサポートし、チップ上に記憶できるデータ量を効果的に2倍にする。32ビット浮動小数点フォーマットと16ビット浮動小数点フォーマットの変換は1つの命令で行われる。

各メモリブロックはコードとデータの組み合わせを格納することができますが、一方のブロックは転送にDMバスを使用してデータを格納し、もう一方のブロックは転送にPMバスを使用して命令とデータを格納する場合、アクセスが最も効率的です。このようにDMバスとPMバスを使用すると、各メモリブロックに1つ専用で、2つのデータ転送でシングルサイクル実行が保証されます。この場合、命令はキャッシュで利用可能でなければなりません。また、ADSP-2106xの外部ポートを介して、データオペランドのいずれかがオフチップと転送されたり、オフチップから転送されたりすると、シングルサイクル実行が維持されます。

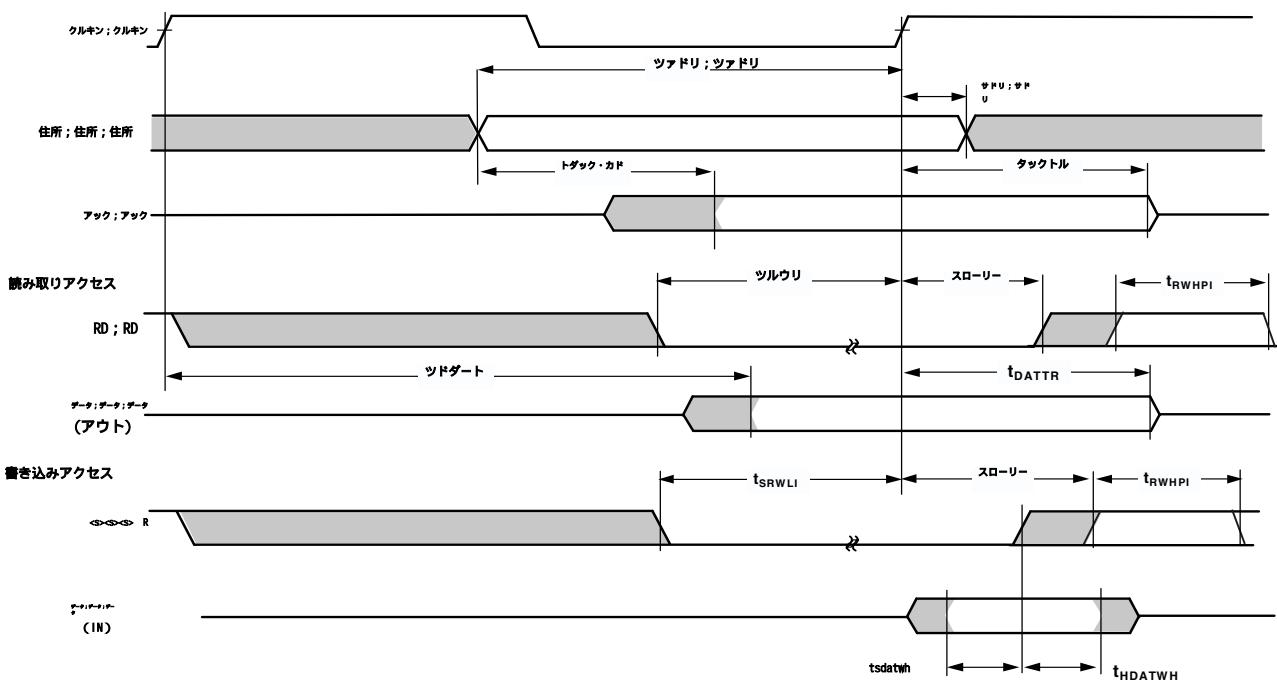

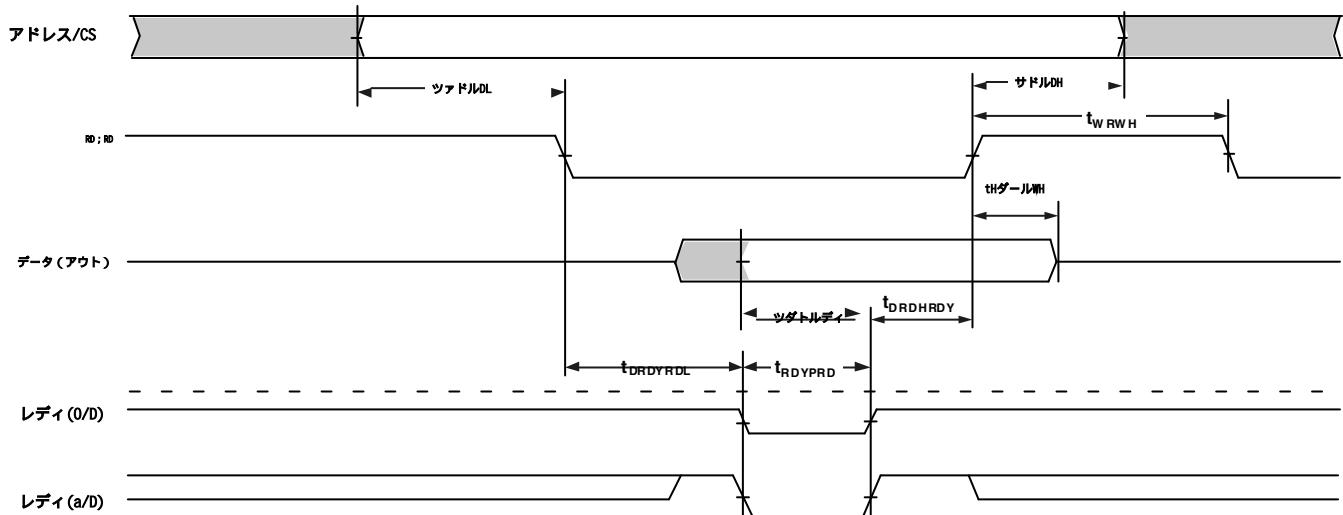

## オンチップメモリおよび周辺機器インターフェース

ADSP-2106xの外部ポートは、オフチップメモリおよび周辺機器へのプロセッサのインターフェースを提供します。4ギガワードのオフチップアドレス空間は、ADSP-2106xの統合されたアドレス空間に含まれます。PMアドレス、PMデータ、DMアドレス、DMデータ、I/Oアドレス、およびI/Oデータのための個別のオンチップバスは、外部ポートで多重され、単一の32ビットアドレスバスと単一の48ビット(または32ビット)データバスを備えた外部システムバスを作成します。

上位アドレス線のオンチップ復号により、外部メモリデバイスのアドレス指定が容易になり、メモリバンクセレクト信号が生成される。ページモードドラムのsimライファイドアドレス指定用にも個別の制御線が生成されます。ADSP-2106xは、プログラム可能なメモリ待機状態と外部メモリ確認制御を提供し、可変アクセス、ホールド、および無効時間要件を備えたドラムおよび周辺機器とのインターフェースを可能にします。

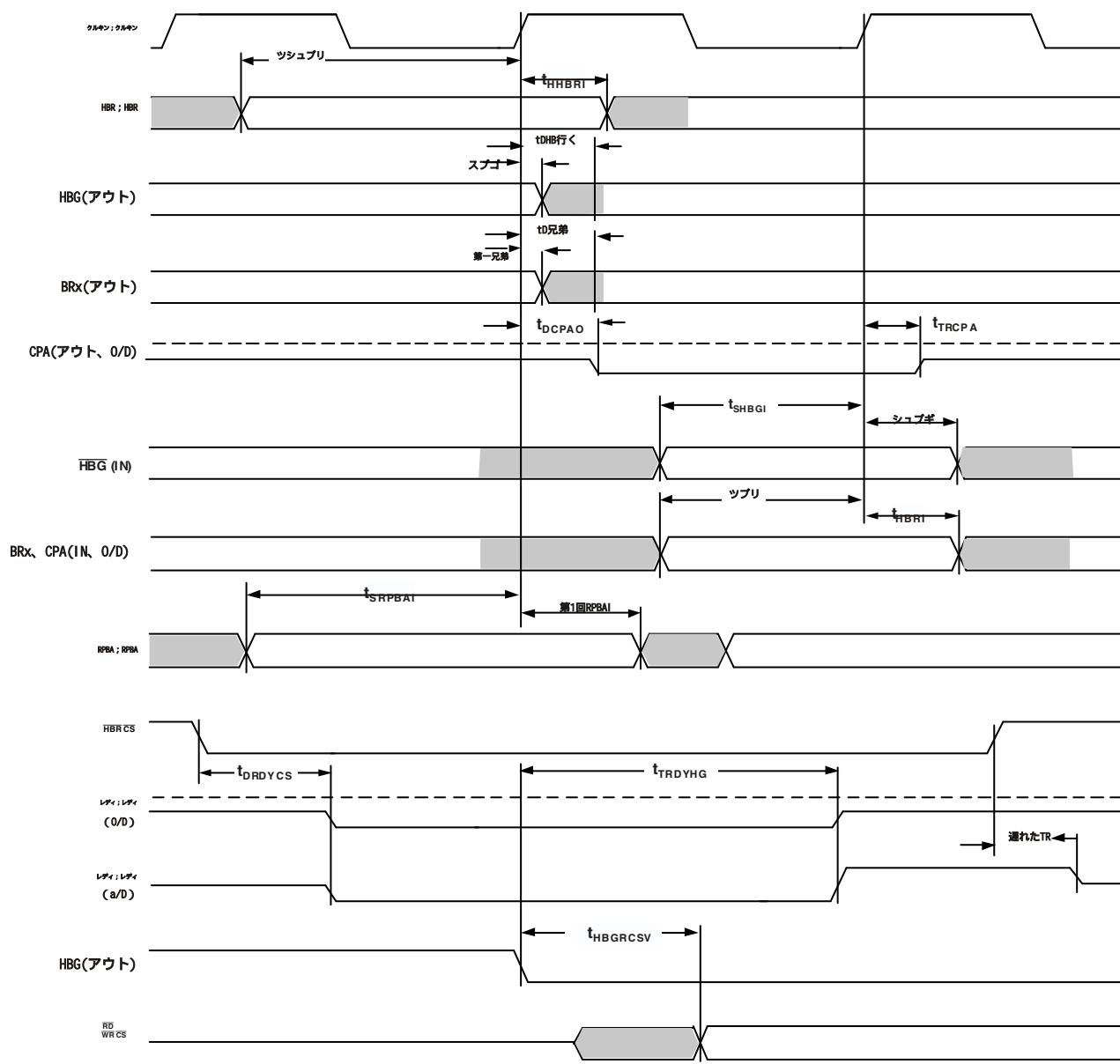

## ホストプロセッサンターフェース

ADSP-2106xのホストインターフェースにより、追加のハードウェアをほとんど必要とせずに、16ビットと32ビットの両方の標準マイクロプロセッサバスに簡単に接続できます。プロセッサのフルクロックレートまでの速度での非同期転送がサポートされています。ホストインターフェースはADSP-2106xの外部ポートを介してアクセスされ、統合されたアドレス空間にメモリマッピングされます。DMAの4つのチャネルは、ホストインターフェースに利用可能です。コードとデータ転送は、低ソフトウェアオーバーヘッドで達成されます。

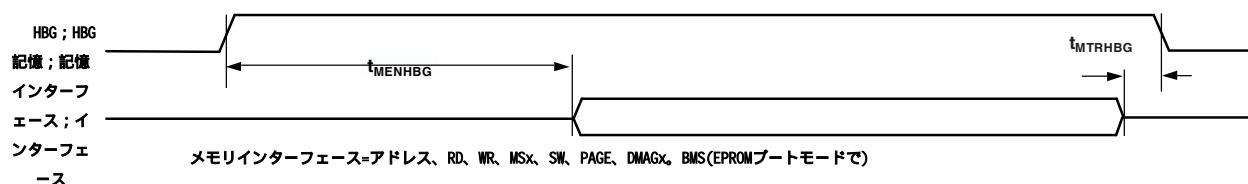

前記ホストプロセッサは、前記ホストバス要求(HBR)、ホストバスグラント(HBG)、およびready(REDY)信号を持つADSP-2106xの外部バスを要求する。ホストはADSP-2106xの内部メモリを直接読み書きでき、DMAチャネルセットアップとメールボックスレジスタにアクセスできます。ベクトル割込みサポートは、ホストコマンドの効率的な実行のために提供されます。

クセスできます。

rev. h 2013年3月64日の5ページ

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

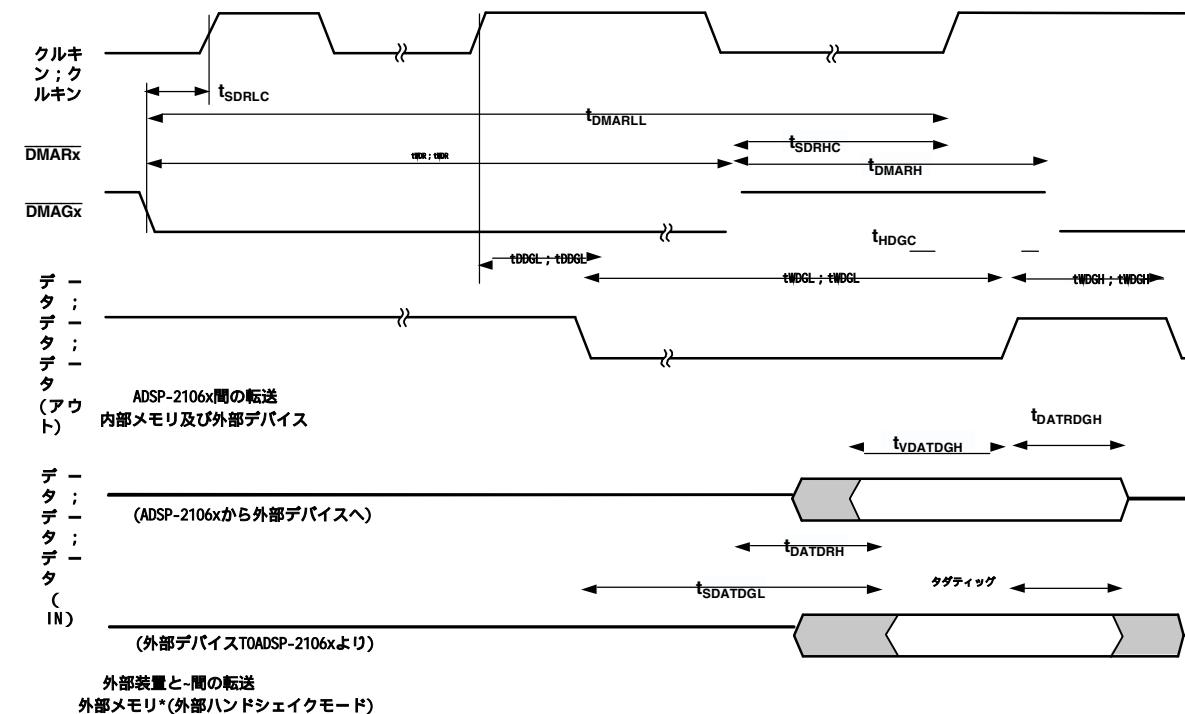

## DMAコントローラ

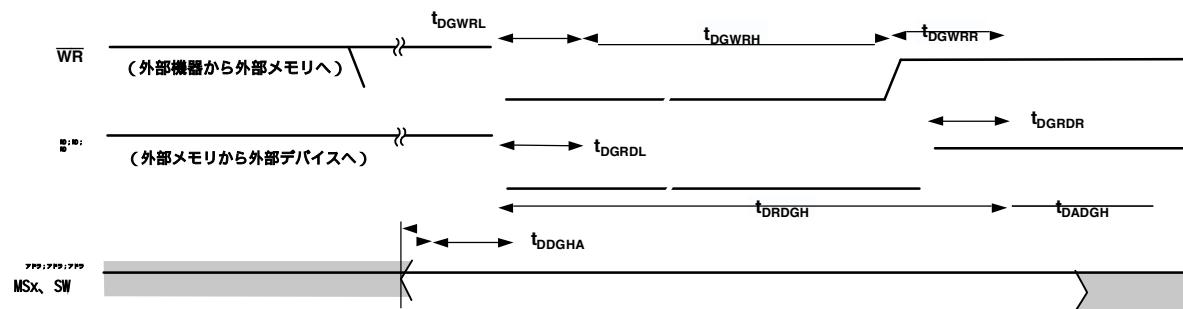

ADSP-2106xのオンチップDMAコントローラは、プロセッサの介入なしにゼロオーバーヘッドデータ転送を可能にします。前記DMAコントローラは、前記プロセッサコアに対して独立して不可視に動作し、前記コアがプログラム命令を同時に実行している間にDMA動作を行うことができる。

ADSP-2106xの内部メモリと外部メモリ、外部周辺機器、またはホストプロセッサの間でDMA転送が発生する可能性があります。adsp-2106xの内部メモリとシリアルポートまたはリンクポートとの間でDMA転送も発生する可能性があります。外部メモリと外部周辺機器間のDMA転送も別のオプションです。外部バスパッキン16-、32ビット、または48ビットワードは、DMA転送中に実行されます。ADSP-2106x-リンクポートを介して2つ、シリアルポートを介して4つ、プロセッサの外部ポートを介して4つのDMAチャネル(ホストプロセッサ、他のADSP-2106xs、メモリ、またはI/O転送のいずれかの場合)で利用可能です。4つの追加リンクポートDMAチャネルがシリアルポート1および外部ポートと共有される。プログラムはDMA転送を使用してADSP-2106xにダウンロードできます。非同期オフチップ周辺機器は、

control two DMA channels using DMA request/grant lines (DMAR1-2, DMAG1-2). Other DMA features include inter-automatic linkingされたDMA転送のためのDMA転送およびDMAチエーンの完了時に突然生成されます。

## 多重処理

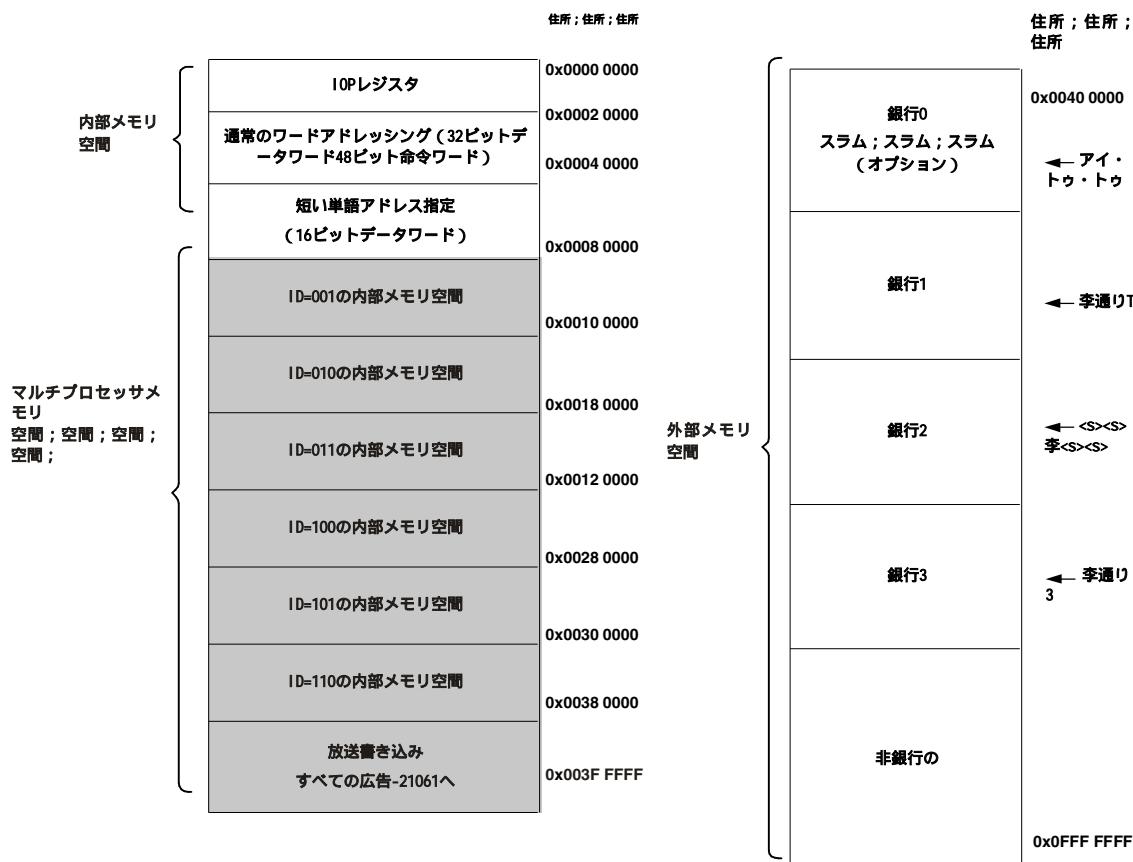

ADSP-2106xは、マルチプロセッサーDSPシステムに合わせた強力な機能を提供します。統合されたアドレス空間(図4を参照)は、各ADSP-2106xの内部メモリの直接プロセッサ間アクセスを可能にします。分散バス調停ロジックは、最大6つのADSP-2106xsとホストプロセッサを含むシステムの簡単で接着剤のない接続のためのオンチップが含まれています。マスタープロセッサの切り替えには、オーバーヘッドが1サイクルしか発生しません。バス仲裁は、固定優先度または回転優先度のいずれかとして選択できます。バスロックにより、セマフォアの読み取り-修正-書き込みシーケンスが不可分になります。プロセッサ間コマンドに対してベクトル割り込みが設けられているプロセッサ間データ転送の最大マムスループットはリンクポートまたは外部ポートを介して240MBイト/秒。ブロードキャスト書き込みは、すべてのADSP-2106xsへのデータの同時送信を可能にし、反射セマフォアを実装するために使用できます。

図4。メモリマップ

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

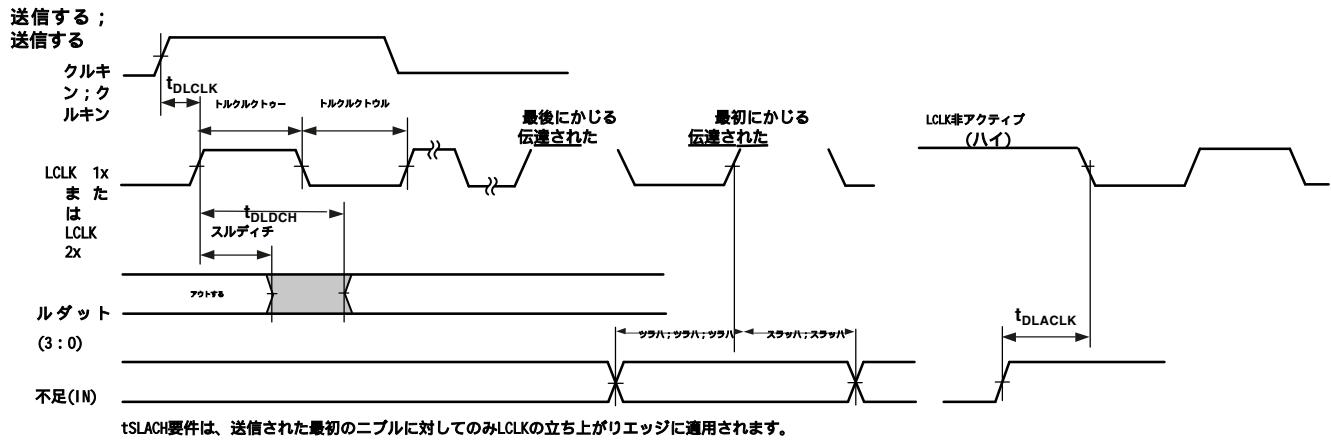

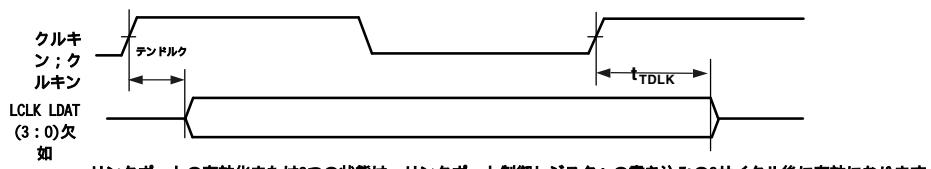

## リンクポート

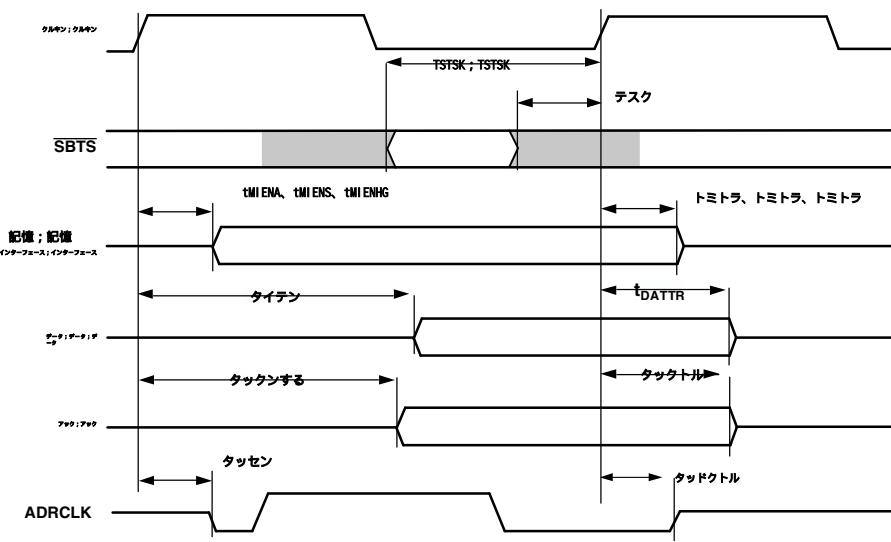

ADSP-2106xは、追加のI/O機能を提供する6つの4ビットリンクポートを備えています。リンクポートは、サイクルごとに2回クロックでき、それぞれがサイクルごとに8ビットのデータを転送することができます。Linkport I/Oは、マルチ処理システムにおけるポイントツーポイントのプロセッサ間通信に特に有用です。

リンクポートは独立して同時に動作し、最大データスループットは240Mバイト/秒です。リンクポートデータは32ビットまたは48ビットワードにパックされ、コアプロセッサで直接読み取るか、オンチップメモリにDMA転送することができます。各リンクポートには、独自のダブルバッファリングされた入出力レジスタがあります。クロック/確認ハンドシェイクコントロールリンクポート転送。転送は、送信または受信のいずれかとしてプログラム可能です。

## プログラム起動

ADSP-2106xの内部メモリは、8ビットEPROM、ホストプロセッサ、またはリンクポートのいずれかを介してシステムパワーアップ時に起動できます。起動ソースの選択は、BMS(起動メモリ選択)、EBOOT(EPROM起動)、およびLBOOT(リンク/ホスト起動)ピンによって制御されます。32ビットおよび16ビットのホスト・プロセッサを起動することができます。前記プロセッサは、前記外部メモリから命令実行をソースとするノーブートモードをポートにもサポートする

## 開発ツール

アナログデバイスは、クロススコア®組み込みスタジオおよび/またはVi sual DSP++®を含む統合開発環境、評価製品、エミュレータ、およびさまざまなソフトウェアアドインを含む、ソフトウェアおよびハードウェア開発ツールの完全なラインでプロセッサをサポートします。

### 統合開発環境(IDEs)

C/C++ソフトウェアの書き込みと編集、コード生成、デバッグサポートのために、アナログデバイスは2つのIDEを提供します。

最新のIDEであるCrossCore Embedded Studioは、EclipseTMフレームワークに基づいています。ほとんどのアナログデバイスがファミリを処理することをサポートしているため、マルチコアデバイスを含む将来のプロセッサにとって選択されています。CrossCore Embedded Studioは、利用可能なソフトウェアアドインをシームレスに統合して、リアルタイムオペレーティングシステム、ファイルシステム、TCP/IPスタック、USBスタック、アルゴリズムソフトウェアモジュール、評価ハードウェアボードサポートパッケージをサポートします。詳細については、[www.analog.com/cces](http://www.analog.com/cces)をご覧ください。

他のアナログデバイスIDEであるVi sual DSPは、CrossCore Embedded Studioのリリース前に導入されたプロセスまたはファミリをサポートしています。このIDEは、アナログデバイスVDKリアルタイムオペレーティングシステムとオープンソースTCP/IPスタックを含む。詳細については、[www.analog.com/vi sual dsp](http://www.analog.com/vi sual dsp)をご覧ください。Vi sual DSPは将来のアナログデバイスプロセッサをサポートしないことに注意してください。

### EZ-KIT Lite評価ボード

プロセッサ評価のために、アナログデバイスは、EZ-KIT Lite®評価ボードを幅広く提供します。プロセッサや第一周辺機器を含め、オンチップにも対応しています。

エミュレーション機能およびその他の評価および開発機能。また、オーディオおよびビデオ処理を含む追加の特殊な機能を提供するドーターカードであるさまざまなEZ-Extenders®も利用できます。詳細については、[www.analog.com](http://www.analog.com)をご覧ください。「ezkit」または「ezextender」で検索してください。

### EZ-KIT Lite評価キット

アナログデバイスプロセッサを使用した開発の詳細については、費用対効果の高い方法で、アナログデバイスはさまざまなオフェズキットライト評価キットを提供しています。各評価キットは、EZ-KIT Lite評価ボードと、利用可能なアイドの評価バージョンのダウンロード方向と、USBケーブルと、電源とを含む。EZ-KIT Liteボード上のUSBコントローラは、ユーザーのPCのUSBポートに接続され、選択されたIDE評価スイートは、オンボードプロセッサの回路内をエミュレートすることができます。これにより、お客様はEZ-KIT Liteシステムのプログラムをダウンロード、実行、およびデバッグできます。また、オンボードフラッシュデバイスの回路内プログラミングをサポートして、ユーザー固有のブートコードを保存し、スタンドアロン操作を可能にします。クロススコア組み込みスタジオまたはVi sual DSP++のフルバージョンをインストール(別売り)すると、エンジニアはサポートされているEZキットまたはサポートされているアナログデバイスプロセッサを利用した任意のカスタムシステム用のソフトウェアを開発できます。

### クロススコア組み込みスタジオ用のソフトウェアアドイン

アナログデバイスは、クロススコア組み込みスタジオをシームレスに格子を組み込み、機能を拡張し、開発時間を短縮するソフトウェアアドインを提供します。アドインには、評価ハードウェア用のボードサポートパッケージ、さまざまなミドルウェアパッケージ、アルゴリズムモジュールが含まれます。これらのアドインに存在するドキュメント、ヘルプ、構成ダイアログ、およびコーディング例は、アドインがインストールされると、クロススコア埋め込みスタジオIDEを介して表示できます。

### 評価ハードウェア用のボードサポートパッケージ

EZ-KIT Lite評価ボードとEZエクステンダー娘カードのソフトウェアサポートは、ボードサポートパッケージ(BSPs)と呼ばれるソフトウェアアドインによって提供されます。BSPsには、必要なドライバ、関連するリリースノート、および指定された評価ハードウェアの例コードを選択しています。特定のBSPのダウンロードリンクは、関連するEZ-KITまたはEZ Extender製品のwebページにあります。リンクは、商品webページの商品ダウンロード領域にあります。

### ミドルウェアパッケージ

アナログデバイスは、リアルタイムオペレーティングシステム、ファイルシステム、USBスタック、TCP/IPスタックなどのミドルウェアアドインを個別に提供します。詳細については、次のwebページを参照してください。

- [www.analog.com/ucos3](http://www.analog.com/ucos3)

- [www.analog.com/ucfs](http://www.analog.com/ucfs)

- [www.analog.com/ucusbd](http://www.analog.com/ucusbd)

- [www.analog.com/lwip](http://www.analog.com/lwip)

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## アルゴリズムモジュール

開発をスピードアップするために、アナログデバイスは一般的なオーディオおよびビデオ処理アルゴリズムを実行するアドインを提供します。これらは、クロススコア埋め込みスタジオとVisual DSPの両方で使用できます。詳細については、[www.analog.com](http://www.analog.com)をご覧ください。「Blackfinソフトウェアモジュール」または「SHARCソフトウェアモジュール」を検索してください。

## エミュレータ対応のDSPボードの設計(ターゲット)

組み込みシステムのテストとデバッグのために、アナログデバイスは一連のエミュレータを提供します。各JTAG DSPで、アナログデバイスはIEEE 1149.1 JTAGテストアクセスポート(タップ)を追加します。回路内エミュレーションは、このJTAGインターフェイスを使用することで容易になります。エミュレータは、プロセッサのタップを介してプロセッサの内部機能にアクセスし、開発者はコードのロード、ブレークポイントの設定、変数、メモリ、およびレジスタの表示を可能にします。データとコマンドを送信するには、プロセッサを停止する必要がありますが、エミュレータによって操作が完了すると、DSPシステムはシステムタイミングに影響を与える前にフルスピードで動作するように設定されます。エミュレータは、ターゲットボードに、DSPのJTAGポートのエミュレータへの接続をサポートするヘッドを含める必要があります。機械的レイアウト、シングルプロセッサー接続、信号バッファリング、信号生成、エミュレータポッドロジックなどのターゲットボード設計の問題の詳細については、アナログデバイスWebサイト([www.analog.com](http://www.analog.com))のEE-68:アナログデバイスJTAGエミュレーション技術参照を参照してください。-「EE-68」でサイト検索を使用してください。このドキュメントは、エミュレータサポートの改善に追いつくために定期的に更新されます。

## 追加情報

このデータシートでは、ADSP-2106xのアーキテクチャと機能の概要を説明します。ADSP-21000ファミリーのコアアーキテクチャと命令セットの詳細については、ADSP-2106x SHARCユーザーマニュアル、リビジョン2.1を参照してください。

## 関連信号鎖

信号チェーンは、入力(リアルタイム現象または保存データからサンプリングしたデータ)をタンデムで受信し、チェーンの一部の出力が次の部分に入力を供給する一連の信号調整電子コンポネントです。信号チェーンは、データを収集して処理したり、リアルタイム現象の分析に基づいてシステム制御を適用したりするために、信号処理アプリケーションでよく使用されます。この用語と関連トピックの詳細については、アナログデバイスWebサイトのEE用語用語集の「信号チェーン」エントリを参照してください。アナログデバイスは、うまく連携するように設計された信号処理コンポーネントを提供することで、信号処理システムの開発を容易にします。特定のアプリケーションと関連コンポーネント間の関係を表示するためのツールは、[www.analog.com](http://www.analog.com) Webサイトで入手できます。

LabTMサイト(<http://www.analog.com/signalchains>)の回路内のアプリケーション信号チェーンページには次のことがあります。

- ? さまざまな回路タイプとアプリケーションの信号チェーンのグラフィカル回路ブロック図表示

- ? 各チェーンのコンポーネントのリンクを選択ガイドとアプリケーション情報にドリルダウンします

- ? ベストプラクティス設計技術を適用した参照設計

## ピン機能の説明

ADSP-2106xピンの定義を以下に示します。同期（複数可）として識別された入力は、CLKIN（またはTMS、TDIのTCKに関して）に関するタイミング要件を満たす必要があります。非同期（a）として識別された入力は、CLKIN（またはTRSTのTCK）に非同期にアサートすることができます。

未使用の入力は、addr31-0、data47-0、flag3-0、および内部プルアップ抵抗またはプルダウン抵抗（CPA、ACK、DTX\_DRX、TCLKx、RCLKx、Ixdat3-0、LxCLK、LxACK、TMS、およびTDI）を備えた入力を除いて、VDDまたはGNDに結合または引っ張る必要があります。これらのピンは浮いたままにすることができます。これらのピンは、入力が内部に浮かぶのを防ぐ論理レベルのホールド回路を備えています。

表3。ピンの説明

| ピン       | タイプ          | 関数                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr31-0 | I/O/T        | 外部バスアドレス。ADSP-2106xは、これらのピンの外部メモリと周辺機器のアドレスを出力します。マルチプロセッサシステムにおいて、前記バスマスターは、他のADSP-2106xsの内部メモリまたはIOPレジスタの読み出し/書き込み用アドレスを出力する、ADSP-2106xは、ホストプロセッサまたはマルチプロセッサバスマスターが内部メモリまたはIOPレジスタを読み書きしているときにアドレスを入力します。                                                                                                                                                                                                          |

| データ47-0  | I/O/T        | 外部バスデータ。ADSP-2106xは、これらのピンのデータと命令を入力および出力します。32ビットの単精度浮動小数点データと32ビットの固定小数点データは、バスのビット47?16を介して転送される。40ビット拡張精度浮動小数点データは、バスのビット47?8を介して転送される。16ビットのショートワードデータは、バスのビット31?16を介して転送される。プロムブートモードでは、ビット23?16を介して8ビットデータが転送されます。未使用のデータピンのプルアップ抵抗は必要ありません。                                                                                                                                                                  |

| MS3-0    | O/T          | メモリ選択行。これらの行は、外部メモリの対応するバンクに対してチップが選択すると（低い）アサートされます。メモリバンクのサイズは、ADSP-2106xのシステムコントロールレジスタ（SYSCON）で定義する必要があります。前記ms3-0線は、他のアドレス線と同時に変化する復号メモリアドレス線である、外部メモリアクセスが発生していない場合、ms3-0ラインは非アクティブです。ただし、条件付きメモリアクセス命令が実行されると、条件が真であるかどうかにかかわらず、それらはアクティブです。MS0をページ信号と一緒に使用して、DRAMメモリのバンク（バンク0）を実装することができます。マルチプロセッショナリシステム3?0ラインはバスマスターによって出力されます。                                                                           |

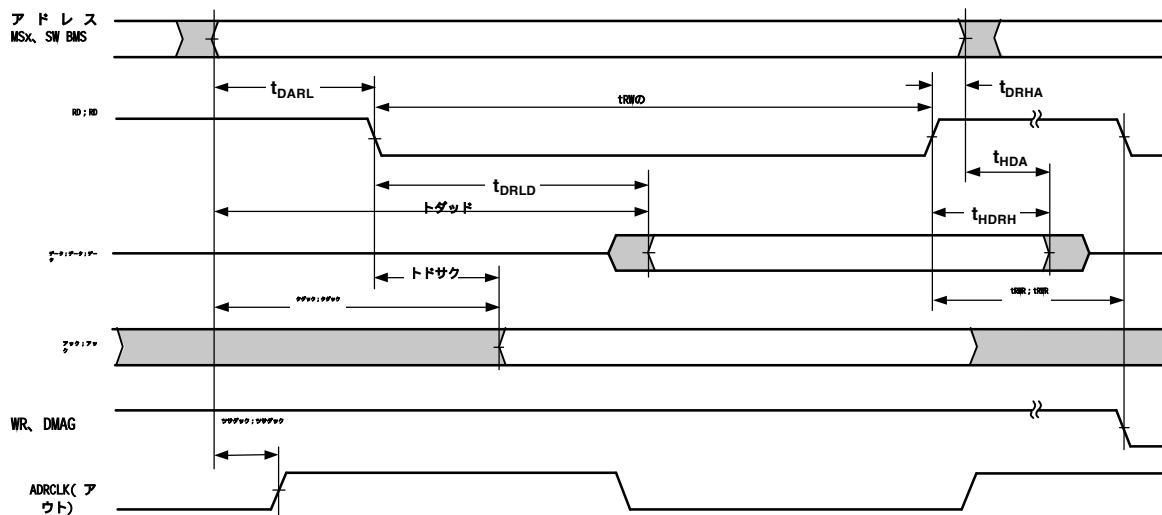

| RD; RD   | I/O/T        | メモリ読み取りストロボ。このピンは、headsp-2106xが外部メモリデバイスまたは他のADSP-2106xsの内部メモリから読み込まれたときに（低い）アサートされます。外部デバイス（他のADSP-2106xsを含む）は、ADSP-2106xの内部メモリから読み取るためにRDをアサートする必要があります。マルチプロセッショナリシステムでは、RDはバスマスターによって出力され、他のすべてのADSP-2106xsによって入力される。                                                                                                                                                                                            |

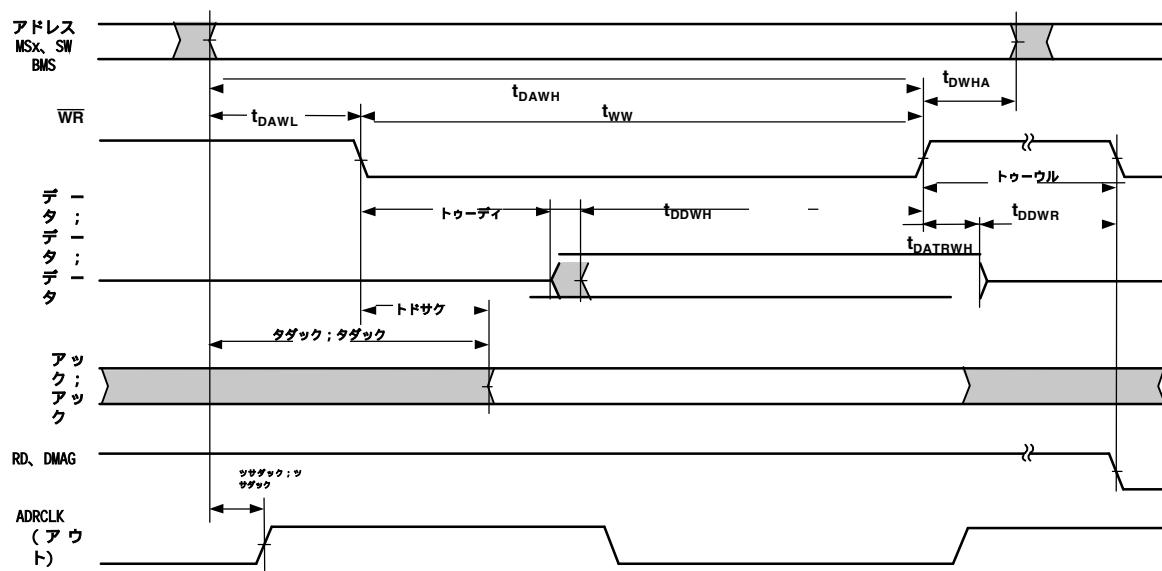

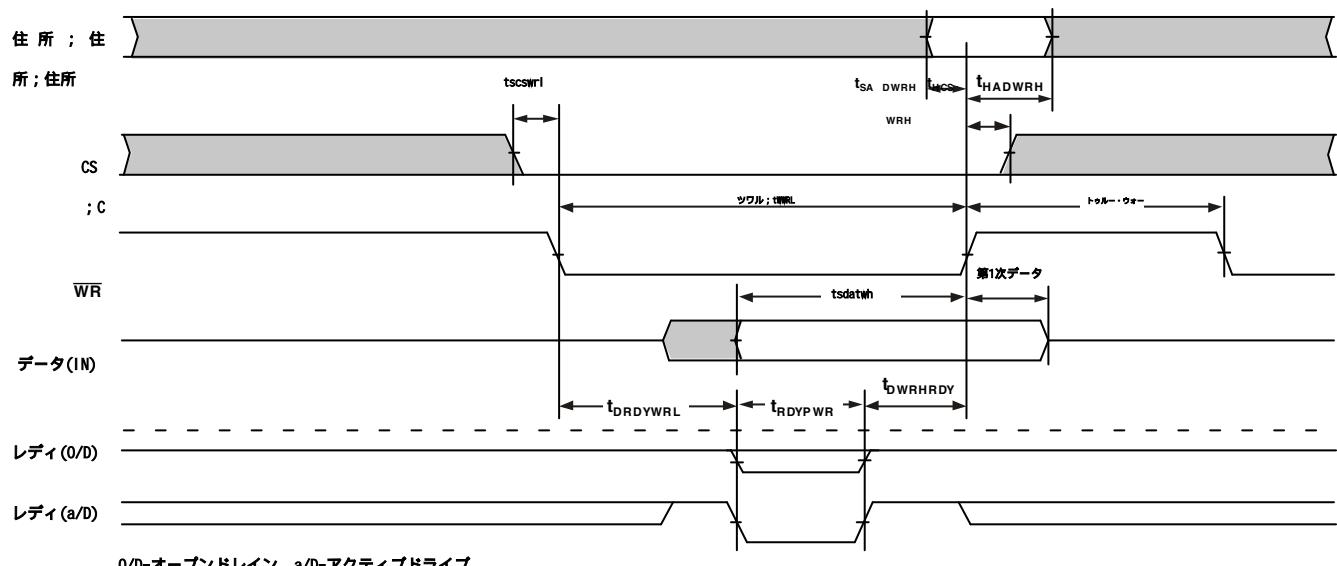

| WR       | I/O/T        | メモリ書き込みストロボ。このピンは、ADSP-2106xが外部メモリデバイスまたは他のADSP-2106xsの内部メモリに書き込むときにアサートされます（低い）。外部デバイスはadsp-2106xの内部メモリに書き込むにはWRをアサートする必要があります。マルチプロセッショナリシステムでは、WRはバスマスターによって出力され、他のすべてのADSP-2106xsによって入力されます。                                                                                                                                                                                                                     |

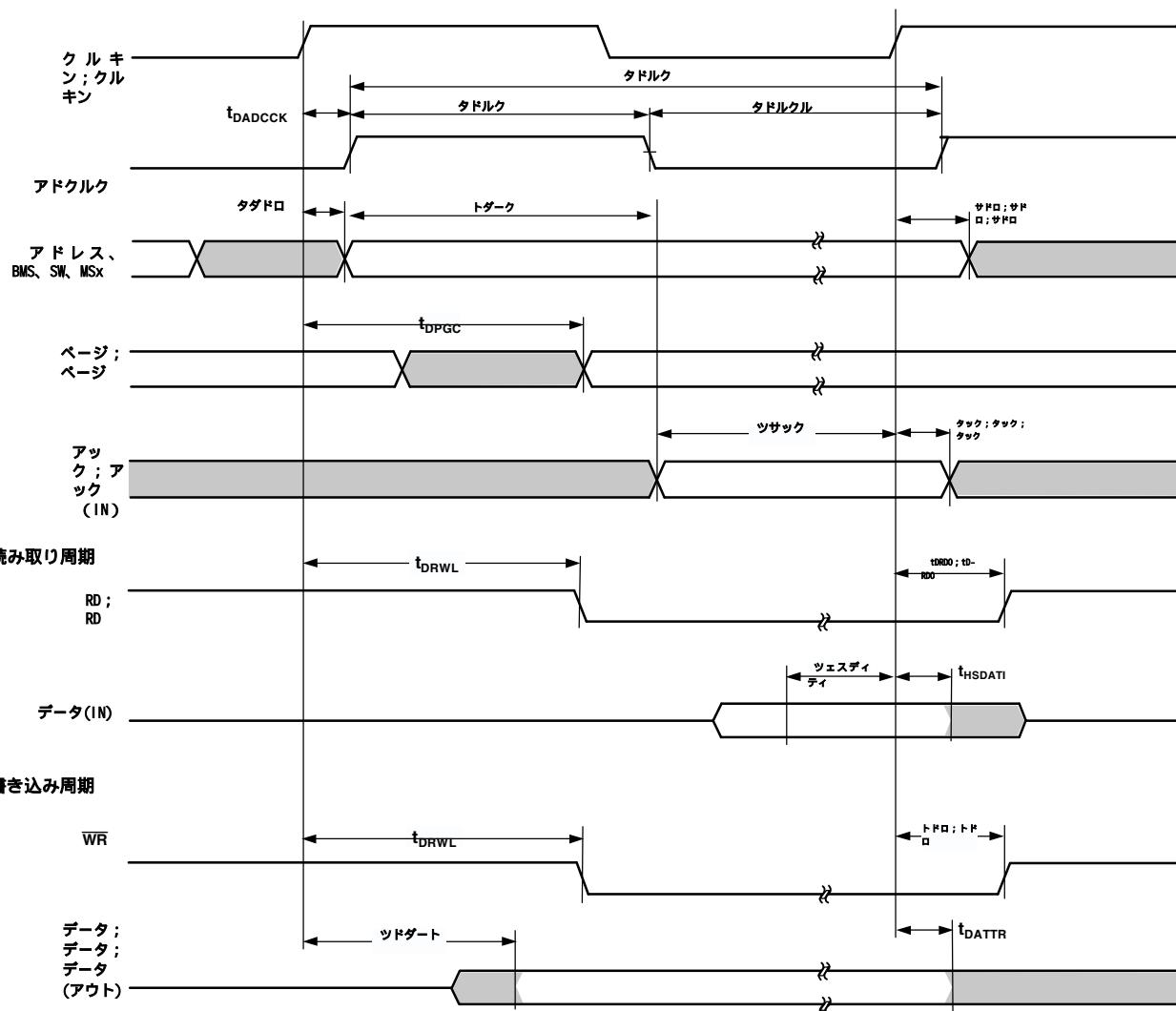

| ページ；ページ  | O/T          | DRAMページの境界。ADSP-2106xは、外部DRAMページの境界が越えられたことをシグナルするためにこのピンを主張します。DRAMページサイズはADSP-2106xのメモリコントロールレジスタ（待機）で定義する必要があります。DRAMは外部メモリバンク0にのみ実装できます。ページ信号は、銀行0アクセスの場合のみ有効にできます。マルチ処理システムでは、バスマスターによってページが出力されます。                                                                                                                                                                                                             |

| ADRCLKSW | O/T<br>I/O/T | クロック出力参照。マルチプロセッショナリシステムにおいて、ADRCLKは、バスマスターによって出力される同期書き込み選択。この信号は、headsp-2106xを同期メモリデバイス（他のADSP-2106xsを含む）にインタフェースするために使用されます。ADSP-2106xは、WRが後でアサートされない場合（条件付き書き込み命令など）中止することができる、差し迫った書き込みサイクルの早期指示を提供するためにSW（LOW）をアサートします。マルチプロセッサシステムにおいて、SWは、バスマスターによって出力され、他のすべてのadsp-2106x上によって入力され、マルチプロセッサメモリアクセスが読み出しましたは書き込みであるかどうかを判断する。SWはアドレス出力と同時にアサートされます。同期書き込みを使用するホストプロセッサは、ADSP-2106xに書き込むときにこのピンをアサートする必要があります。 |

a=非同期、G=グランド、I=入力、O=出力、P=電源、S=同期、(a/D)=アクティブドライブ、(0/D)=オーブンドレイン、T=3

状態(SBTSがアサートされた場合、またはADSP-2106xがバススレーブの場合)

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

表3。ピンの説明(続き)

| ピン                                     | タイプ            | 関数                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| アック ; アック                              | I/O/S          | 記憶が認めます。外部デバイスはACK(IOW)を解除して、外部メモリアクセスに待機状態を追加できます。ACKは、外部メモリアクセスの完了を阻止するために、I/Oデバイス、メモリコントローラ、またはその他の周辺機器によって使用されます。ADSP-2106xは、内部メモリの同期アクセスに待機状態を追加するための出力としてACKをデアサートします。マルチプロセッショングシステムにおいて、スレーブADSP-2106xは、バスマスターのACK入力をデアサートして、その内部メモリのアクセスに待機状態を追加する。バスマスターには、アクピンにキーパーラッチが付いており、入力を最後に駆動したレベルに維持します。                    |

| <u>SBTS</u>                            | I/S            | バス3州を停止します。外部デバイスは、次のサイクルのために、外部バスアドレス、データ、選択、およびストローブを高インピーダンス状態に配置するためにSBTS(IOW)をアサートすることができます。ADSP-2106xがSBTSがアサートされている間に外部メモリにアクセスしようとすると、プロセッサは停止し、SBTSがデアサートされるまでメモリアクセスは完了しません。SBTSは、ホストプロセッサ/ADSP-2106xデッドロックからのリカバリにのみ使用するか、DRAMコントローラで使用する必要があります。                                                                    |

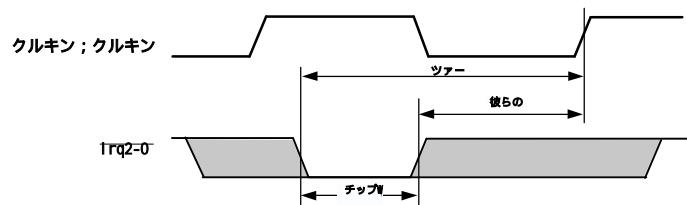

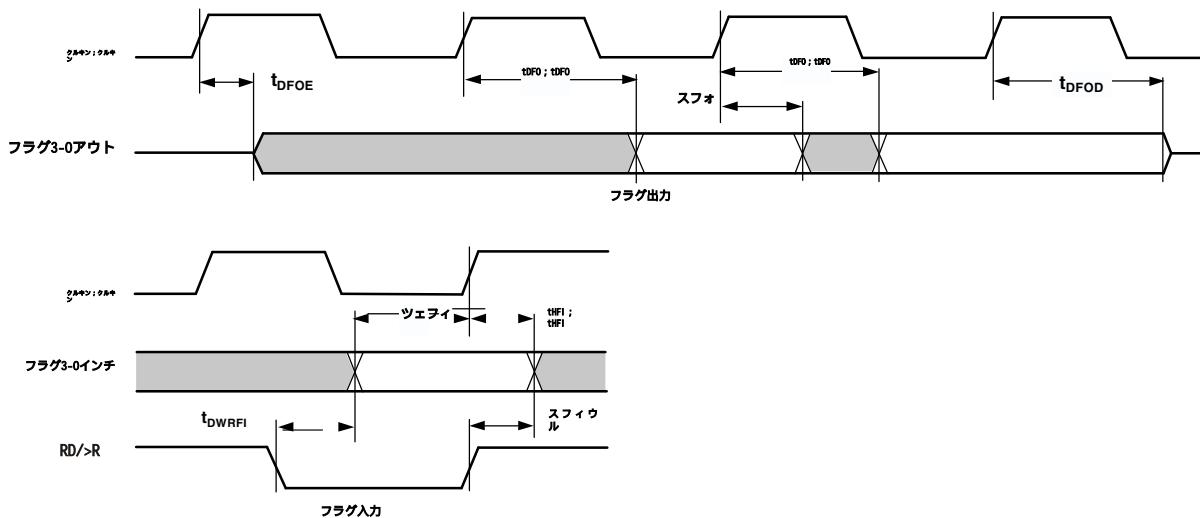

| <u>Irq2-0フラグ3-0</u>                    | I/A<br>I/O/A   | 要求行を割り込みます。エッジトリガーまたはレベル敏感のいずれかであってもよいです。 フラグピン。それぞれは、入力または出力のいずれかの制御ビットを介して構成される、入力として、条件としてテストすることができます。出力として、外部周辺機器に信号を送るために使用できます。                                                                                                                                                                                          |

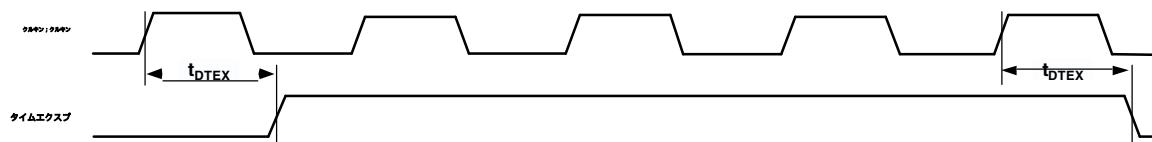

| <u>タイムエクスパンション</u><br><u>HBR ; HBG</u> | 0.<br>I/A      | タイマーの有効期限が切れました。タイマーが有効になっており、TCOUNTがゼロに減少したときに4サイクルアサートされます。ホストバスリクエスト。ADSP-2106xの外部バスの制御を要求するには、このピンはホストプロセッサによってアサートされなければなりません。マルチプロセッショングシステムでHBRがアサートされると、バスマスターであるADSP-2106xはバスを放棄してHBGをアサートします。バスを放棄するには、ADSP-2106xは、アドレス、データ、セレクト、ストップボラインを高インピーダンス状態に置きます。HBRは、マルチプロセッショングシステムにおけるすべてのADSP-2106xバス要求br6-1よりも優先されています。 |

| <u>HBG ; HBG</u>                       | I/O            | ホストバス助成金。前記ホストプロセッサが前記外部バスを制御してもよいことを示すバス要求を認識するHBGisは、HBRがリリースされるまでheadsp-2106xによって主張されました(低く保持されました)。Inaマルチプロセッショングシステム、HBGはADSP-2106xバスマスターによって出力され、他のすべてによって監視されます。                                                                                                                                                         |

| <u>CSレディ</u>                           | I/A<br>0 (0/D) | チップを選択します。ホストプロセッサがADSP-2106xを選択するように主張しました。                                                                                                                                                                                                                                                                                    |

| <u>Dmar2-I</u>                         | I/A            | ホストバスが承認します。TheADSP-2106xは、ホストによる内部メモリまたはIOPレジスタの非同期アクセスに待機状態を追加するために、READY(IOW)を解除します。このピンはデフォルトでオープンドレイン出力(0/D)です。SYSCONレジスタのADREADYビットにアクティブドライブ(a/D)にプログラムできます。READYはCSとHBRの入力がアサートされた場合にのみ出力されます。                                                                                                                          |

| <u>Dmag2-1 br6-1</u>                   | O/T<br>I/O/S   | DMAリクエスト1(DMAチャネル7)およびDMAリクエスト2(DMAチャネル8)。<br>DMAグラント1(DMAチャネル7)およびDMAグラント2(DMAチャネル8)。                                                                                                                                                                                                                                          |

| <u>Td2-0</u>                           | 0 (0/D)        | マルチ処理バスリクエスト。バスマスター・シップ用のマルチプロセッショングADSP-2106xtoアービトレートで使用されます。ADSP-2106xは、独自のBRxライン(ID2-0入力の値に対応する)のみを駆動し、他のすべてを監視します。6つ未満のADSP-2106xsのマルチプロセッサーシステムでは、未使用のBRxピンを高く引っ張る必要があります。プロセッサ独自のBRxラインは出力であるため、高くも低くも引っ張ってはなりません。                                                                                                       |

| <u>RPBA ; RPBA</u>                     | I/S            | マルチプロセシングID。ADSP-2106xで使用されるマルチ処理バスリクエスト(br1-br6)を決定します。シングルプロセッサシステムにおけるID=001はBR1、ID=010はBR2等ID=000に相当する。これらの回線は、ハードウェイーまたはリセット時にのみ変更する必要があるシステム構成の選択です。                                                                                                                                                                      |

| <u>CPA ; CPA</u>                       | I/O (0/<br>D)  | 回転優先バス調停を選択します。RPBAが高い場合、マルチプロセッサバス調停のための回転優先度が選択されます。RPBAが低い場合は、固定優先度が選択されます。この信号は、すべてのADSP-2106xで同じ値に設定する必要があるシステム構成の選択です。システム動作中にRPBAの値が変更された場合は、ADSP-2106xごとに同じCLKINサイクルで変更する必要があります。                                                                                                                                       |

| <u>DTx ; DTX</u>                       | O/I/O          | コア優先アクセス。そのCPAピンを主張すると、anADSP-2106xバススレーブのコアプロセッサがバックグラウンドDMA転送を中断し、外部バスにアクセスすることができます。CPAは、システム内のすべてのADSP-2106xsに接続されているオープンドレイン出力です。前記CPAピンは、内部に5kΩのプルアップ抵抗を有する、システムでコアアクセス優先度が必要ない場合は、CPAピンを接続しないままにする必要があります。                                                                                                               |

| <u>DRxTCLKx</u>                        | I/O            | データ送信(シリアルポート0、1)。各DTピンは、50kΩの内部プルアップ抵抗を有しています。                                                                                                                                                                                                                                                                                 |

| <u>RCLKx</u>                           |                | データ受信(シリアルポート0、1)。各DRピンは50kΩの内部プルアップ抵抗を有しています。                                                                                                                                                                                                                                                                                  |

---

|  |                                                          |

|--|----------------------------------------------------------|

|  | す。<br>受信クロック(シリアルポート0、1)。各RCLKピンは、50k の内部プルアップ抵抗を有しています。 |

|--|----------------------------------------------------------|

---

a=非同期、G=グランド、I=入力、O=出力、P=電源、S=同期、(a/D)=アクティブドライブ、(O/D)=オープンドレイン、T=3

状態(SBTSがアサートされた場合、またはADSP-2106xがバススレーブの場合)

---

rev. h 2013年3月64日の11ページ

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

表3。ピンの説明(続き)

| ピン                                                                                                          | タイプ                                                          | 関数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------|-------|-------|---|---|--------|--------------------------------|---|---|--------|----------|---|---|--------|--------|---|---|--------|------------------------------------|---|---|-------|-------|---|---|--|-------|

| TFSx ; TFSX<br>RFSx<br>Lxdat3-0<br>LxCLK<br>ルクサック<br>イーブート<br>イルブート<br><br>BMS ; BMS                        | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I.<br>I.<br>I/OT   | <p>送信フレーム同期(シリアルポート0、1)。<br/> <b>フレーム同期を受信します(シリアルポート0、1)。</b><br/> リンクポートデータ(リンクポート0-5)。各LxDATピンには、LCOMレジスタのLPDRDビットによって有効または無効にされる50 k の内部プルダウン抵抗があります。<br/> リンクポートクロック(リンクポート0-5)。各LxCLKピンには、LCOMレジスタのLPDRDビットによって有効または無効にされる50 k の内部プルダウン抵抗があります。<br/> リンクポートを確認します(リンクポート0-5)。各LxACKピンには、LCOMレジスタのLPDRDビットによって有効または無効にされる50 k の内部プルダウン抵抗があります。<br/> EPROMブートを選択します。EB00Tが高い場合、headsp-2106xは8ビットEPROMから起動するように構成されます。EB00Tが低い場合、LBO0T入力とBMS入力により起動モードが決定されます。以下のBMSピンの説明の表を参照してください。この信号は、ハードワイヤーにする必要があるシステム構成選択です。<br/> リンク起動。LBO0Tが高い場合、ADSP-2106xはリンクポートの起動用に構成されます。LBO0Tが低い場合、ADSP-2106xはホストプロセッサが起動するか、起動しないように構成されます。以下のBMSピンの説明の表を参照してください。この信号は、ハードワイヤーにする必要があるシステム構成選択です。<br/> 起動メモリを選択します。出力：boot EPROMデバイスのチップセレクトとして使用されます(EB00T=1、LBO0T=0の場合)。マルチプロセッサシステムでは、前記バスマスターによってBMSが出力されるInput：低い場合は、起動が発生しないことを示し、ADSP-2106xが外部メモリから命令の実行を開始します。以下の表を参照してください。この入力は、ハードワイヤーにする必要があるシステム構成の選択です。*3-epromブートモード(BMSが出力の場合)でのみステート可能です。</p> <table border="0"> <thead> <tr> <th>イーブ<br/>ート</th> <th>イルブ<br/>ート</th> <th>BMS出力</th> <th>起動モード</th> </tr> </thead> <tbody> <tr> <td>1</td> <td>0</td> <td>1 (入力)</td> <td>EPROM(BMSをEPROMチップに接続して選択します。)</td> </tr> <tr> <td>0</td> <td>0</td> <td>1 (入力)</td> <td>ホストプロセッサ</td> </tr> <tr> <td>0</td> <td>1</td> <td>0 (入力)</td> <td>リンクポート</td> </tr> <tr> <td>0</td> <td>0</td> <td>0 (入力)</td> <td>起動はありません。プロセッサは、外部メモリから実行される。予約された</td> </tr> <tr> <td>0</td> <td>1</td> <td>x(入力)</td> <td>予約された</td> </tr> <tr> <td>1</td> <td>1</td> <td></td> <td>予約された</td> </tr> </tbody> </table> <p>クリキン；クリキン<br/><br/>リセットする</p> <p>時計が入ります。ADSP-2106xへの外部クロック入力。命令サイクルレートはCLKINに等しい。CLKINは、指定された最小周波数以下で停止、変更、または操作してはなりません。</p> <p>プロセッサのリセット。前記ADSP-2106xを既知の状態にリセットし、前記ハードウェアリセットペクトルアドレスで指定されたプログラムメモリ位置でプログラム実行を開始する、この入力は、電源アップ時に(低)アサートする必要があります。</p> <p>テストクロック(JTAG)。JTAG境界スキャン用の非同期クロックを提供します。</p> <p>テストモードSelect(JTAG)。テスト状態マシンを制御するために使用されます。TMSは20k 内部プルアップ抵抗を備えています。テストデータ入力(JTAG)。境界スキャンロジックのシリアルデータを提供します。TDIは20k 内部プルアップ抵抗を有する。</p> <p>テストデータ出力(JTAG)。前記境界走査バスのシリアル走査出力と、</p> <p>テストリセット(JTAG)。テスト状態マシンをリセットします。ADSP-2106xを適切に動作させるには、電源投入後にTRSTをアサート(パルス低く)するか、低く保持する必要があります。TRSTは20k の内部プルアップ抵抗を有している。</p> <p>エミュレーションステータス。ADSP-2106x EZ-ICEターゲットボードコネクタにのみ接続する必要があります。</p> <p>電源；5 Vデバイスの場合は5.0 V dc、3.3 Vデバイスの場合は3.3 V dcです。(30ピン)。</p> <p><b>電源リターン。(30ピン)。</b></p> <p>接続しないでください。開いて接続されていないままにする必要がある予約済みのピン。</p> | イーブ<br>ート                          | イルブ<br>ート | BMS出力 | 起動モード | 1 | 0 | 1 (入力) | EPROM(BMSをEPROMチップに接続して選択します。) | 0 | 0 | 1 (入力) | ホストプロセッサ | 0 | 1 | 0 (入力) | リンクポート | 0 | 0 | 0 (入力) | 起動はありません。プロセッサは、外部メモリから実行される。予約された | 0 | 1 | x(入力) | 予約された | 1 | 1 |  | 予約された |

| イーブ<br>ート                                                                                                   | イルブ<br>ート                                                    | BMS出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 起動モード                              |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 1                                                                                                           | 0                                                            | 1 (入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EPROM(BMSをEPROMチップに接続して選択します。)     |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 0                                                                                                           | 0                                                            | 1 (入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ホストプロセッサ                           |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 0                                                                                                           | 1                                                            | 0 (入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | リンクポート                             |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 0                                                                                                           | 0                                                            | 0 (入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 起動はありません。プロセッサは、外部メモリから実行される。予約された |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 0                                                                                                           | 1                                                            | x(入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 予約された                              |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| 1                                                                                                           | 1                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 予約された                              |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

| TCKTMSTDI<br><br>TDO ; TDO<br><br>トランジスト；トランジ<br>スト<br><br>△<br>ICSA ; ICSA ;<br>ICSA<br>VDD ; VDD<br>GNDNC | I/A<br>I/S<br>I/S<br>0.<br>I/A<br>0.<br>0.<br>P ; P<br>G ; G | <p>プロセッサのリセット。前記ADSP-2106xを既知の状態にリセットし、前記ハードウェアリセットペクトルアドレスで指定されたプログラムメモリ位置でプログラム実行を開始する、この入力は、電源アップ時に(低)アサートする必要があります。</p> <p>テストクロック(JTAG)。JTAG境界スキャン用の非同期クロックを提供します。</p> <p>テストモードSelect(JTAG)。テスト状態マシンを制御するために使用されます。TMSは20k 内部プルアップ抵抗を備えています。テストデータ入力(JTAG)。境界スキャンロジックのシリアルデータを提供します。TDIは20k 内部プルアップ抵抗を有する。</p> <p>テストデータ出力(JTAG)。前記境界走査バスのシリアル走査出力と、</p> <p>テストリセット(JTAG)。テスト状態マシンをリセットします。ADSP-2106xを適切に動作させるには、電源投入後にTRSTをアサート(パルス低く)するか、低く保持する必要があります。TRSTは20k の内部プルアップ抵抗を有している。</p> <p>エミュレーションステータス。ADSP-2106x EZ-ICEターゲットボードコネクタにのみ接続する必要があります。</p> <p>電源；5 Vデバイスの場合は5.0 V dc、3.3 Vデバイスの場合は3.3 V dcです。(30ピン)。</p> <p><b>電源リターン。(30ピン)。</b></p> <p>接続しないでください。開いて接続されていないままにする必要がある予約済みのピン。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |           |       |       |   |   |        |                                |   |   |        |          |   |   |        |        |   |   |        |                                    |   |   |       |       |   |   |  |       |

a=非同期、G=グランド、I=入力、O=出力、P=電源、S=同期、(a/D)=アクティブドライブ、(0/D)=オープンドレイン、T=3

状態(SBTSがアサートされた場合、またはADSP-2106xがバススレーブの場合)

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## EZ-ICEプローブ用ターゲットボードコネクタ

adsp-2106x ez-ice®エミュレータは、ADSP-2106xのIEEE 1149.1 jtagテストアクセスポートを使用して、エミュレーション中にターゲットボードプロセッサを監視および制御します。EZ-ICEプローブには、ADSP-2106xのCLKIN、TMS、TCK、TRST、TDI、TDO、EMU、およびGND信号が14ピンコネクタ(2行7ピンストリップヘッダー)を介してターゲットシステム上でアクセスできるようにする必要があります。図5に示すような、EZ-ICEプローブは、チップオンボードエミュレーションのためにこのコネクタに直接接続されます。ADSP-2106x EZ-ICEを使用する場合は、このコネクタをターゲットボード設計に追加する必要があります。保証された動作のために、EZ-ICEコネクタとEZ-ICE JTAGピンを共有する最も遠いデバイスとの間のトレース長は最大15インチに制限する必要があります。この長さ制限には、1つ以上のADSP-2106xデバイス、またはチェーン上のADSP-2106xデバイスと他のJTAGデバイスの組み合わせにルーティングされるEZ-ICE JTAG信号が含まれなければなりません。

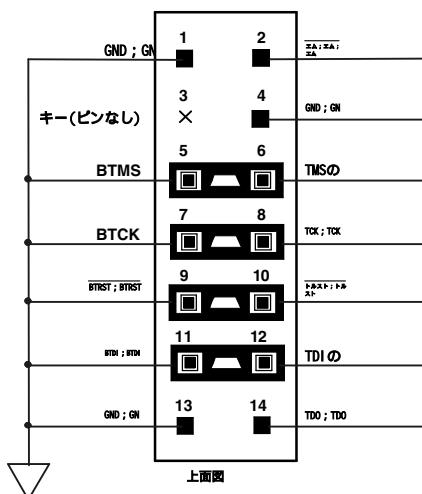

図5. ターゲットボードコネクタforADSP-2106x EZ-ICEエミュレータ

(ジャンパーは所定の位置にあります)

14ピン2行のピンストリップヘッダーは、ピン3位置にキー付けされています。ピン3はヘッダから取り外されなければなりません。ピンは0.025インチ正方形で、長さは少なくとも0.20インチでなければなりません。ピン間隔は0.1 × 0.1インチでなければなりません。ピンストリップヘッダーは、3M、McKenzie、Samtecなどのベンダーから入手できます。前記BTMS、BTCK、BTRST、およびBTDI信号は、前記テストアクセスポートを基板レベルのテストにも使用することができるよう提供されます。コネクタがエミュレーションに使用されていない場合は、図5に示すようにBxxxピンにジャンパーを配置します。ボードテストにテストアクセスポートを使用しない場合は、BTRSTをGNDに結び付け、BTCKをVDDに結び付けるかプルアップします。adsp-2106xを適切に動作させるには、電源アップ後(コネクタのBTRSTを介して)TRSTピンをアサート(パルス低く)するか、低く保持する必要があります。Bxxxピン(ピン5、7、9、11)はいずれもEZ-ICEプローブに接続されていません。

JTAG信号は、表4に示すように、EZ-ICEプローブ上で終了する。

表4. コア命令率/CLKIN比選択

| 信号                | 終了；終了                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------|

| TMSの<br>TCK ; TCK | 10 MHzで駆動される22 抵抗(16 mAドライバ)を駆動し、22 抵抗(16 mAドライバ)を駆動します。                                      |

| TRST <sup>1</sup> | 22 抵抗(16 mAドライバ)で駆動される22 抵抗(16 mAドライバ)で駆動されるオンチップ20 k 抵抗でプルアップされたアクティブドライブ                    |

| TDIの<br>TDO ; TDO | 1つのTTL負荷、分割終了(160/220)<br>1つのTTL負荷、分割終端(160/220)アクティブ低4.7k プルアップ抵抗、1つのTTL負荷(DSPからのオープンドレイン出力) |

| 2ルキン：クル<br>王ム：エム： |                                                                                               |

<sup>1</sup>ソフトウェア起動時にEZ-ICEプローブがエミュレータによってオンになるまで、TRSTsを低く駆動します。ソフトウェアの起動後、高く駆動されます。

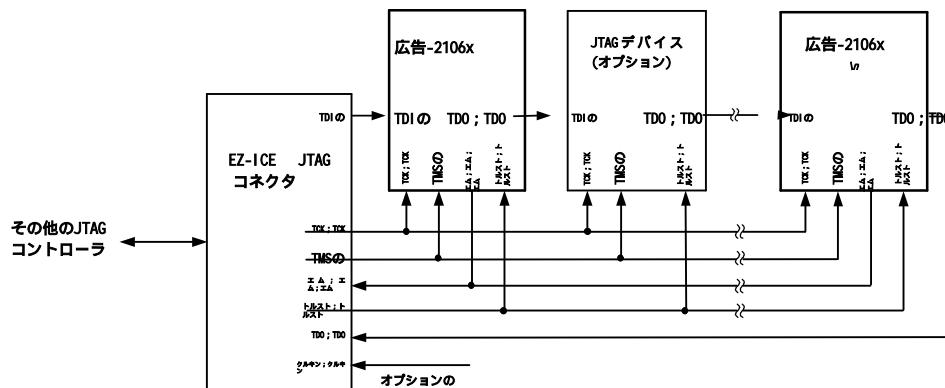

図6は、複数のADSP-2106xプロセッサを含むシステムのJTAGスキヤンパス接続を示しています。

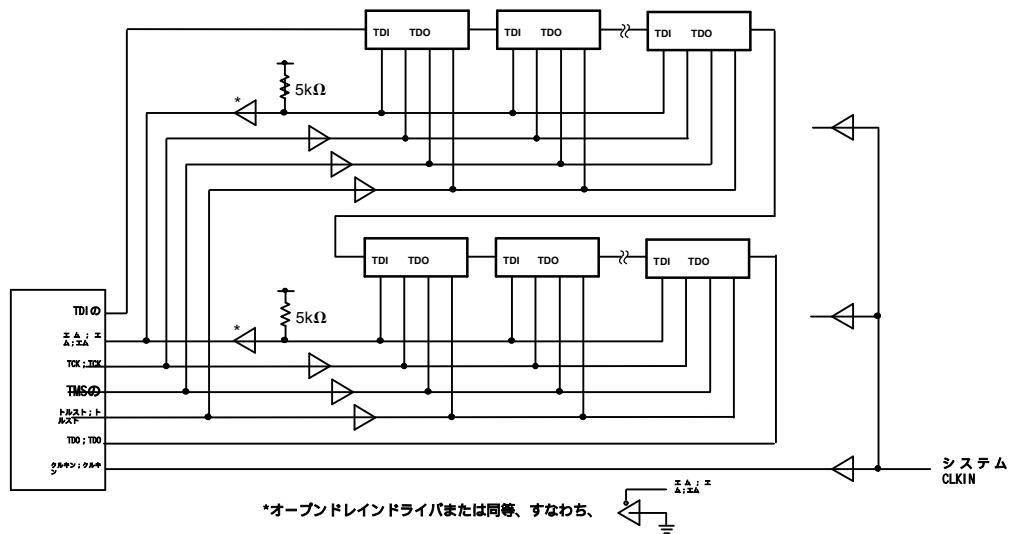

CLKINをEZ-ICEヘッダーのピン4に接続することはオプションです。エミュレータは、複数のADSP-2106xsを同期的に開始、停止、單一ステップで実行するように指示された場合にのみCLKINを使用します。複数のプロセッサでこれらの操作を同期して実行する必要がない場合は、EZ-ICEヘッダーのピン4をグランドに結び付けるだけです。同期マルチプロセッサ操作が必要で、CLKINが接続されている場合、複数のADSP-2106xプロセッサとEZ-ICEヘッダー上のCLKINピンとの間のクロックスキューは最小限でなければなりません。スキューが大きすぎると、同期動作がプロセッサ間で1つ以上のサイクルオフになる可能性があります。同期マルチプロセッサ操作の場合、TCK、TMS、CLKIN、およびEMUはスキューの観点から重要な信号として扱われ、ボード上でできるだけ短くレイアウトする必要があります。TCK、TMS、およびCLKINがシステム内で多数のADSP-2106xs(8つ以上)を駆動している場合は、複数のドライバを使用してそれらを「クロックツリー」として扱い、スキューを最小限に抑えます。(図7およびADSP-2106xユーチューバーマニュアル、リビジョン2.1の「高周波設計の考慮事項」セクションの「JTAGクロックツリー」および「クロック分布」を参照してください。)

同期マルチプロセッサ操作が必要ない場合(つまりCLKINが接続されていない場合)は、TCKとTMSで適切な並列終了を使用するだけです。TDI、TDO、EMU、TRSTは、スキューの観点から重要な信号ではない。

SHARC EZ-ICEの完全な情報については、ADSP-21000ファミリーJTAG EZ-ICEユーザーガイドと参照を参照してください。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

図6。複数のADSP-2106xシステムのJTAGスキャンバス接続

図7。複数のADSP-2106xシステム用のJTAGクロックツリー

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## ADSP-21060/ADSP-21062仕様

コンポーネントの仕様は予告なしに変更される場合

がありますのでご注意ください。

### 運転条件 (5v)

| パラメータ; パラメータ                         | 説明               | 1つの成績 |         | Cグレード |         | Kグレード |         | ユニット |

|--------------------------------------|------------------|-------|---------|-------|---------|-------|---------|------|

|                                      |                  | 分:分   | 最大; 最大  | 分:分   | 最大; 最大  | 分:分   | 最大; 最大  |      |

| VDD; VDD                             | 電源電圧             | 4.75  | 5.25    | 4.75  | 5.25    | 4.75  | 5.25    | V.   |

| チップラスター;<br>チップラスター:                 | ケース動作温度          | -40   | +85     | -40   | +100    | -40   | +85     | °C   |

| V <sub>IH</sub> <sup>1</sup><br>ビ-22 | 高レベル入力電圧@VDD=Max | 2.0   | VDD 0.5 | 2.0   | VDD 0.5 | 2.0   | VDD 0.5 | V.   |

| 悪1、2                                 | 高レベル入力電圧@VDD=Max | 2.2   | VDD 0.5 | 2.2   | VDD 0.5 | 2.2   | VDD 0.5 | V.   |

|                                      | 低レベル入力電圧@VDD=Min | -0.5  | +0.8    | -0.5  | +0.8    | -0.5  | +0.8    | V.   |

1 入力ピンと双方向ピンに適用されます : data47-0, addr31-0, RD, WR, SW, ACK, SBTS, irq2-0, flag3-0, HBG, CS, DMAR1, DMAR2, br6-1, id2-0, RPBA, CPA, TFS0, TFS1, RFS0, RFS1, lxdat3-0, LxCLK, LxACK, EBOOT, LBOOT, BMS, TMS, TDI, TCK, HBR, DRO, DR1, TCLK0, TCLK1, RCLK1, RCLK1。

2 入力ピン : CLKIN, RESET, TRSTに適用されます。

### 電気特性(5v)

| パラメータ; パラメータ                                                  | 説明       | 試験条件                           | 分:分 | 最大; 最大 | ユニット   |

|---------------------------------------------------------------|----------|--------------------------------|-----|--------|--------|

| V <sub>OH</sub> <sup>1, 2</sup><br>VOL1、2                     | 高レベル出力電圧 | @VDD=Min, IOH=-2.0 mA          | 4.1 |        | V.     |

| I <sub>IL</sub> <sup>3</sup><br>I <sub>ILP</sub> <sup>4</sup> | 低レベル出力電圧 | @VDD=Min, IOL=4.0mA            |     | 0.4    | V.     |

| I <sub>OZH</sub> <sup>5, 6, 7, 8</sup><br>アイオズル               | 高レベル入力電流 | @VDD=最大, VIN=VDD最大             |     | 10     | μA     |

| I <sub>OZL</sub> <sup>5, 9</sup><br>アイオジ                      | 低レベル入力電流 | @VDD=最大, VIN=0 V               |     | 10     | μA     |

| ヨビ-9<br>ヨウズル                                                  | 低レベル入力電流 | @VDD=最大, VIN=0 V               |     | 150    | μA     |

| ク7<br>ヨウズラ10                                                  | 三状態漏れ電流  | @VDD=最大, VIN=VDD最大             |     | 10     | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=0 V               |     | 10     | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=0 V               |     | 350    | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=0 V               |     | 1.5    | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=1.5V              |     | 350    | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=0 V               |     | 4.2    | μA     |

| ヨズラル8                                                         | 三状態漏れ電流  | @VDD=最大, VIN=0 V               |     | 150    | μA     |

| CIN11、12                                                      | 入力容量     | フイン=1mhz, TCASE=25°C, VIN=2.5V |     | 4.7    | pF; pF |

1 出力および双方向ピンに適用されます : data47-0, ADDR31-0, ms3-0, RD, WR, PAGE, ADRCLK, SW, ACK, flag3-0, TIMEXP, HBG, REDY, DMAG1, DMAG2, br6-1, CPA, DTO, DT1, TCLK0, TCLK1, RCLK1, TFS0, TFS1, RFS0, RFS1, lxdat3-0, LxCLK, LxACK, BMS, TDO, EMU, ICSA。

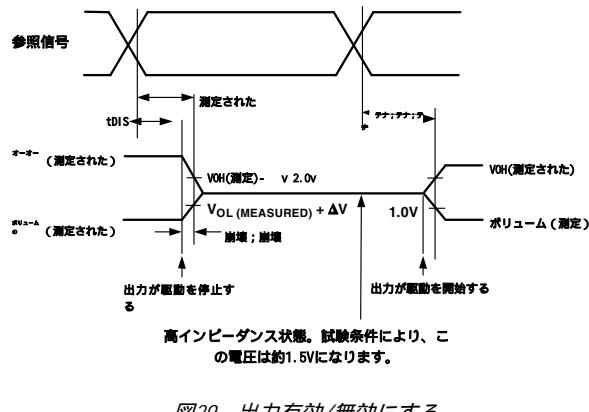

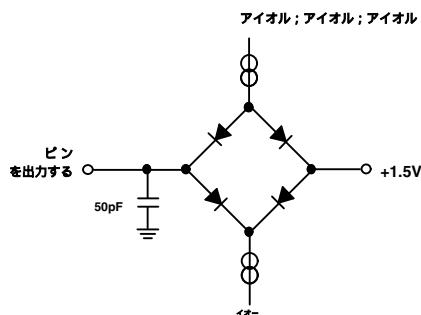

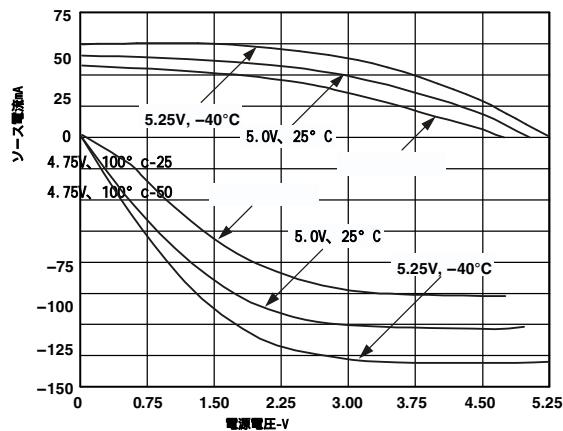

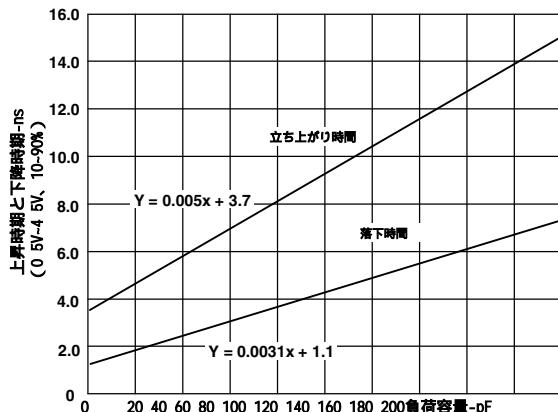

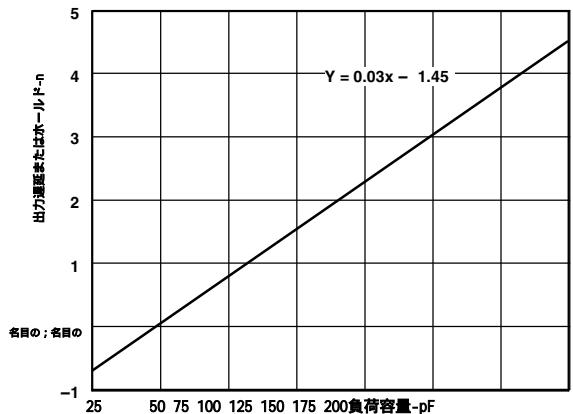

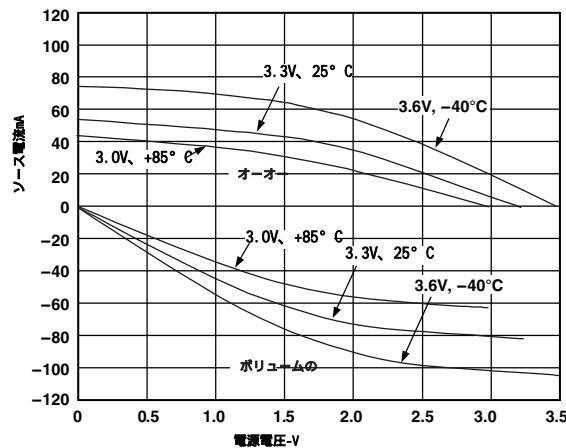

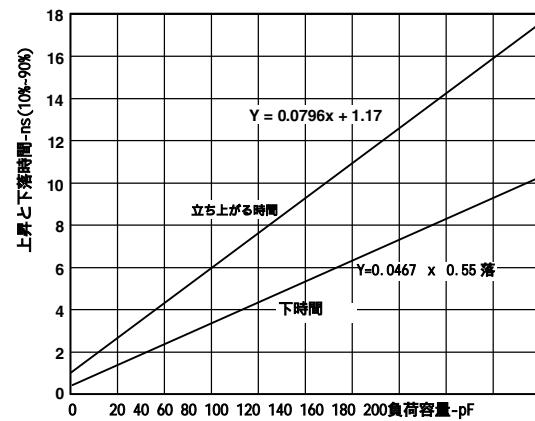

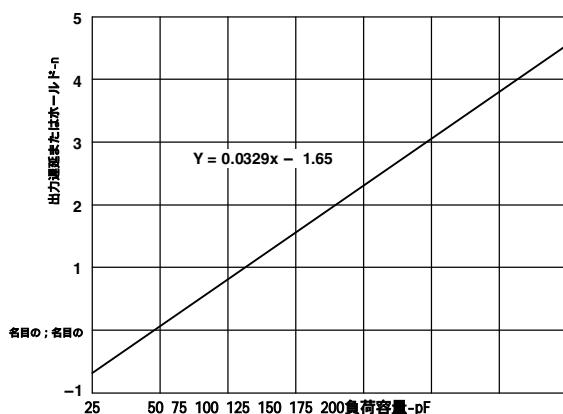

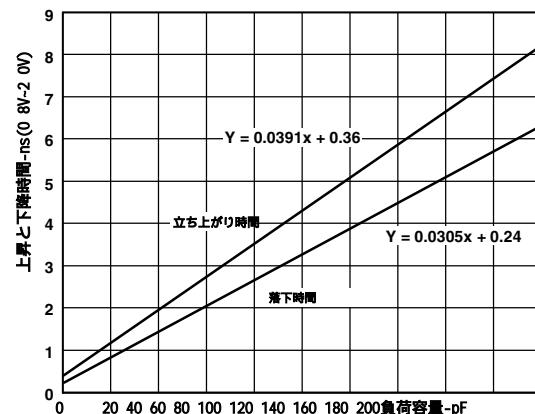

2 一般的な駆動電流能力については、図31、出力駆動電流5 Vを参照してください。

3 入力ピンに適用されます : ACK, SBTS, irq2-0, HBR, CS, DMAR1, DMAR2, id2-0, RPBA, EBOOT, LBOOT, CLKIN, RESET, TCK。

4 内部プルアップ付きの入力ピン : DRO, DR1, TRST, TMS, TDIに適用されます。

5 data47-0, addr31-0, ms3-0, RD, WR, PAGE, ADRCLK, SW, ACK, flag3-0, HBG, REDY, DMAG1, DMAG2, BMS, br6-1, TFS0, RFS0, TD0, EMUの3つのステート可能なピンに適用されます。(マルチプロセッサシステムでは、id2-0=001と別のADSP-2106xがバスマスタシップを要求していない場合、リセット中に、ACKが内部的に2kΩで引き上げられることに注意してください。)

6 内部プルダウンを備えた3つのステート可能なピンに適用されます : DTO, DT1, TCLK0, TCLK1, RCLK0, RCLK1。

7 CPAピンに適用されます。

8 引っ張ったときにACKピンに適用されます。(マルチプロセッサシステムでは、id2-0=001と別のADSP-2106xLがバスマスタシップを要求していない場合、リセット中に、ACKが内部的に2kΩで引き上げられることに注意してください。)

9 内部プルダウンを備えた3つのステート可能なピンに適用されます : lxdat3-0, LxCLK, LxACK。

10は、キーパーラッチが有効になった場合に、ACKピンに適用される。

11は、すべての信号ピンに適用される。

12保証されていますが、テストされていません。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 内部消費電力 (5v)

これらの仕様は、VDDの内部電源部分にのみ適用されます。消費電力を測定するために使用されるコードの詳細については、テクニカルノート「シャーク消費電力測定」を参照してください。

仕様は動作シナリオに基づいています。

| 手術        | ピーク活動(IDDINPEAK) | 高い活動性(IDDINHIGH) | アクティビティが低い(IDDINLOW) |

|-----------|------------------|------------------|----------------------|

| 命令タイプ     | 多機能の             | 多機能の             | 単一関数                 |

| 命令取り込み    | キャッシュ            | 内部記憶装置           | 内部記憶装置               |

| コアメモリアクセス | 2サイクルごと(DMとPM)   | 1サイクルあたり(DM)     | なし                   |

| 内部記憶DMA   | 1サイクルごとに         | 12サイクルごとに        | 12サイクルごとに            |

特定のアプリケーションの消費電力を推定するには、次の方程式を使用します。%は、その状態でプログラムが費やす時間です。

$$\% \text{ ピーク } IDDINPEAK + \% \text{ 高 } IDDINHIGH + \% \text{ 低 } IDDINLOW + \% \text{ アイドル} / IDDIDLE = \text{消費電力}$$

| パラメータ；パラメータ        | 試験条件                           | 最大；最大 | ユニット |

|--------------------|--------------------------------|-------|------|

| IDDINPEAK供給電流(内部)1 | tCK=30ns、V <sub>DD</sub> =Max  | 745   | ママ；母 |

|                    | tCK=25 ns、V <sub>DD</sub> =Max | 850   | ママ；母 |

| IDDINHIGH供給電流(内部)2 | tCK=30ns、V <sub>DD</sub> =Max  | 575   | ママ；母 |

|                    | tCK=25 ns、V <sub>DD</sub> =Max | 670   | ママ；母 |

| IDDINLOW供給電流(内部)2  | tCK=30ns、V <sub>DD</sub> =Max  | 340   | ママ；母 |

|                    | tCK=25ns、V <sub>DD</sub> =Max  | 390   | ママ；母 |

| アイドル供給電流(アイドル)3    | V <sub>DD</sub> = Max          | 200   | ママ；母 |

<sup>1</sup> IDDINPEAKを測定するために使用されるテストプログラムは、最悪の場合のプロセッサ動作を表し、通常のアプリケーション条件下では持続可能ではありません。一般的なアプリケーションを使用して行われた実際の内部電力測定値は指定されていません。

<sup>2</sup> IDDINHIGHは、高アクティビティコードの範囲に基づく複合平均です。IDDINLOWは、範囲oflowアクティビティコードに基づく複合平均です。

<sup>3</sup> Idleは、Idle命令の実行中のADSP-2106x状態を表します。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 外部消費電力 (5v)

総消費電力は、内部回路によるものと外部出力ドライバの切り替えによるものの2つの構成要素である。内部電力消費は、計測実行シーケンスと関係するデータオペランドに依存している。内部消費電力は次のように算出されます。

$$\text{ピント} = \text{IDDIN} \times VDD$$

総消費電力の外部成分は、出力ピンの切り替えによって生じます。その大きさは次のものによって異なります。

- ? 各サイクル中に切り替える出力ピンの数(0)

- ? 切り替えることができる最大周波数(f)

- ? それらの負荷容量(C)

- ? 彼らの電圧スイング(VDD)

- そして次のように計算されます。

$$P_{EXT} = O \times C \times V_{DD}^2 \times f$$

負荷容量には、プロセッサのパッケージ容量(CIN)が含まれる必要があります。前記スイッチング周波数は、前記負荷を高く駆動した後、低く戻すことを含む、アドレスピンとデータピンは

最大1/(2tCK)の速度で高値と低値を駆動します。前記書き込みストロボは、周期毎に1/tCKの周波数で切り替えることができる、選択ピンは1/(2tCK)でスイッチしますが、選択は各サイクルをオンにすることができます。例：次の仮定でPEXTを推定します。

- ? 1つの外部データメモリラム(32ビット)を備えたシステム

- ? 128K × 8ラムチップが4つ使用され、それぞれの負荷があります。

- 10 pF

- ? 外部データメモリの書き込みは、1/(4tCK)のレートで別のサイクルごとに発生し、ピンの50%が切り替わります。

- ? 命令サイクルレートは40 MHz(tCK=25 ns)であり、PEXT方程式は、駆動できるピンのクラスごとに計算されます。

典型的な内部消費電力を追加することで、これらの条件のために典型的な消費電力を計算することができるようになりました。

$$PTOTAL = PEXT(IDDIN2 \times 5.0V)$$

最悪のケースのペストを引き起こす条件は、最悪のケースのパイントを引き起こす条件とは異なることに注意してください。出力ピンの100%がすべてのピンからすべてのゼロに切り替わっている間、最大パイントは発生することはできません。また、アプリケーションでは、出力の100%または50%が同時に切り替わることは一般的ではないことに注意してください。

表5. 外部電力計算 (5vデバイス)

| ピン型   | ピンの数 | %切り替え | × C      | × f     | × vdd2 | = P <sub>EXT</sub> |

|-------|------|-------|----------|---------|--------|--------------------|

| アドレス  | 15   | 50    | × 44.7pf | × 10mhz | × 25v  | =0.084W            |

| MS0   | 1    | 0     | × 44.7pf | × 10mhz | × 25v  | =0.000W            |

| WR    | 1    | -     | × 44.7pf | × 20mhz | × 25v  | =0.022W            |

| データ   | 32   | 50    | × 14.7pf | × 10mhz | × 25v  | =0.059W            |

| アドクルク | 1    | -     | × 4.7pf  | × 20mhz | × 25v  | =0.002W            |

$$pext=0.167W$$

## **ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC**

## ADSP-21060L/ADSP-21062L仕様

コンポーネントの仕様は予告なく変更される場合がありますのでご注意ください。

### 運転条件 (3.3v)

| パラメータ ; パラメータ                         | 説明               | 1つの成績     |         | Cグレード     |         | Kグレード     |         | ユニット |

|---------------------------------------|------------------|-----------|---------|-----------|---------|-----------|---------|------|

|                                       |                  | 分 ; 分 ; 分 | 最大 ; 最大 | 分 ; 分 ; 分 | 最大 ; 最大 | 分 ; 分 ; 分 | 最大 ; 最大 |      |

| VDD ; VDD                             | 電源電圧             | 3.15      | 3.45    | 3.15      | 3.45    | 3.15      | 3.45    | V.   |

| タップタップス:<br>タップタップス                   | ケース動作温度          | -40       | +85     | -40       | +100    | -40       | +85     | °C   |

| V <sub>H</sub> 1 <sup>1</sup><br>ビ-22 | 高レベル入力電圧@VDD=Max | 2.0       | VDD 0.5 | 2.0       | VDD 0.5 | 2.0       | VDD 0.5 | V.   |

|                                       | 高レベル入力電圧@VDD=Max | 2.2       | VDD 0.5 | 2.2       | VDD 0.5 | 2.2       | VDD 0.5 | V.   |

| 悪1、2                                  | 低レベル入力電圧@VDD=Min | -0.5      | +0.8    | -0.5      | +0.8    | -0.5      | +0.8    | V.   |

1 入力ピンと双方向ピンに適用されます：data47-0, addr31-0, RD, WR, SW, ACK, SBTS, irq2-0, flag3-0, HGB, CS, DMAR1, DMAR2, br6-1, id2-0, RP-BA, CPA, TFS0, TFS1, RFS0, RFS1, lxdat3-0, LxCLK, LxACK, EBOOT, LBOOT, BMS, TMS, TDI, TCK, HBR, DRO, DR1, TCLK0, TCLK1, RCLK1, RCLK1。

<sup>2</sup>入力ピン：CLKIN、RESET、TRSTに適用されます。

電氣特性(3.3v)

1出力および双方向ピンに適用されます: data47-0、addr3T-0、ms3-0、RD、WR、PAGE、ADRLCK、SW、ACK、flag3-0、TIMEXP、HBG、REDY、DMAGT、DMAG2、br6-1、CPA、DTO、DT1、TCLK0、TCLK1、RCLK1、RCLK1、TFS0、TFS1、RF50、RFS1、Ixdat3-0、LxCLK、LxACK、BMS、TDO、EMU、ICSA。

一般的な駆動電流能力については、図35、出力駆動電流3.3Vを参照してください。

<sup>3</sup> 入力ピンに適用されます : ACK, SBTS, irq2-0, HBR, CS, DMAR1, DMAR2, i d2-0, RPBA, EBOOT, LB00T, CLKIN, RESET, TCK。

4 内部プルアップ付きの入力ピン：DIO、DIR1、TRST、TMS、TDIに適用されます。

5 data47-0, \_addr31-0, ms3-0, RD, WR, PAGE, ADRCLK, SW, ACK, f1ag3-0, HBG, REDY, DMAG1, DMAG2, BMS, br6-1, TFSX, RFXS, TDO, EMUの3つのステート可能なピンに適用されます。（マルチプロセッサシステムでは、id2=0=001と別のADSP-2106xがバスマスターシップを要求していない場合、リセット中に、ACKは内部的に2kで引き上げられることに注意してください。）

6 内部プルアップ付きの3つのステータブルピンに適用されます： DTO、DT1、TCLK0、TCLK1、RCLK0、RCLK1。

7 CPAピンに適用されます。

<sup>8</sup>引っ張ったときにACKピンに適用されます。（マルチプロセッサシステムでは、id2-0=001と別のADSP-2106xLがバスマスタシップを要求していない場合、リセット中に、ACKが内部的に2kで引き上げられることに注意してください）。

内部プルダウンを備えた3つのステート可能なピンに適用されます：Ixdat3-0、LxCLK、LxACK。

10は、キーパーラッチが有効になった場合に、ACKピンに適用される。

11は、すべての信号ピンに適用される。

12保証されていますが、テストされていません。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 内部消費電力 (3.3v)

これらの仕様は、VDDの内部電源部分にのみ適用されます。消費電力を測定するために使用されるコードの詳細については、テクニカルノート「シャーク消費電力測定」を参照してください。

仕様は動作シナリオに基づいています。

| 手順        | ピーク活動(IDDINPEAK) | 高い活動性(IDDINHIGH) | アクティビティが低い(IDDINLOW) |

|-----------|------------------|------------------|----------------------|

| 命令タイプ     | 多機能の<br>キャッシュ    | 多機能の<br>内部記憶装置   | 単一関数                 |

| 命令取り込み    | 2サイクルごと(DMとPM)   | 1サイクルあたり(DM)     | 内部記憶装置               |

| コアメモリアクセス | 1サイクルごとに         | 12サイクルごとに        | なし                   |

| 内部記憶DMA   |                  |                  | 12サイクルごとに            |

特定のアプリケーションの消費電力を推定するには、次の方程式を使用します。%は、その状態でプログラムが費やす時間です。

$$\% \text{ピーク} IDDINPEAK + \% \text{高} IDDINHIGH + \% \text{低} IDDINLOW + \%$$

アイドル IDDIDLE = 消費電力

| パラメータ ; パラメータ      | 試験条件               | 最大 ; 最大 | ユニット   |

|--------------------|--------------------|---------|--------|

| IDDINPEAK供給電流(内部)1 | tCK=30ns、V DD=Max  | 540     | ママ ; 母 |

|                    | tCK=25ns、V DD=Max  | 600     | ママ ; 母 |

| IDDINHIGH供給電流(内部)2 | tCK=30ns、V DD=Max  | 425     | ママ ; 母 |

|                    | tCK=25 ns、V DD=Max | 475     | ママ ; 母 |

| IDDINLOW供給電流(内部)2  | tCK=30ns、V DD=Max  | 250     | ママ ; 母 |

|                    | tCK=25 ns、V DD=Max | 275     | ママ ; 母 |

| アイドル供給電流(アイドル)3    | VDD = Max          | 180     | ママ ; 母 |

1 IDDINPEAKを測定するために使用されるテストプログラムは、最悪の場合のプロセッサ動作を表し、通常のアプリケーション条件下では持続可能ではありません。一般的なアプリケーションを使用して行われた実際の内部電力測定値は指定されていません。

2 IDDINHIGHは、アクティビティの高いコードの範囲に基づく複合平均です。IDDINLOWは、範囲oflowアクティビティコードに基づく複合平均です。

3 Idleは、Idle命令の実行中のADSP-2106xL状態を表します。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## 外部消費電力 (3.3v)

総消費電力は、内部回路によるものと外部出力ドライバの切り替えによるものの2つの構成要素である。内部電力消費は、計測実行シーケンスと関係するデータオペランドに依存している。内部消費電力は次のように算出されます。

$$\text{ピント} = \text{IDDIN} \times V_{DD}$$

総消費電力の外部成分は、出力ピンの切り替えによって生じます。その大きさは次のものによって異なります。

- ? 各サイクル中に切り替える出力ピンの数(0)

- ? 切り替えることができる最大周波数(f)

- ? それらの負荷容量(C)

- ? 彼らの電圧スイング(VDD)

そして次のように計算されます。

$$P_{EXT} = O \times C \times V_{DD}^2 \times f$$

負荷容量には、プロセッサのパッケージ容量(CIN)が含まれる必要があります。前記スイッチング周波数は、前記負荷を高く駆動した後、低く戻すことを含む、アドレスピンとデータピンは

最大 $1/(2tCK)$ の速度で高値と低値を駆動します。前記書き込みストロボは、周期毎に $1/tCK$ の周波数で切り替えることができる、選択ピンは $1/(2tCK)$ でスイッチしますが、選択は各サイクルをオンにすることができます。

例：次の仮定でPEXTを推定します。

- ? 1つの外部データメモリラム(32ビット)を備えたシステム

- ? 128K × 8ラムチップが4つ使用され、それぞれの負荷があります。

- 10 pF

- ? 外部データメモリの書き込みは、 $1/(4tCK)$ のレートで別のサイクルごとに発生し、ピンの50%が切り替わります。

- ? 命令サイクルレートは40 MHz( $tCK=25$  ns)であり、PEXT方程式は、駆動できるピンのクラスごとに計算されます。

典型的な内部消費電力を追加することで、これらの条件のために典型的な消費電力を計算することができるようになりました。

$$P_{TOTAL} = P_{EXT}(IDDIN2 \times 3.3V)$$

最悪のケースのペストを引き起こす条件は、最悪のケースのパイントを引き起こす条件とは異なることに注意してください。出力ピンの100%がすべてのピンからすべてのゼロに切り替わっている間、最大パイントは発生することはできません。また、アプリケーションでは、出力の100%または50%が同時に切り替わることは一般的ではないことに注意してください。

表6。外部電力計算(3.3vデバイス)

| ピン型   | ピンの数 | %切り替え | xC       | xf      | x vdd2  | =pext   |

|-------|------|-------|----------|---------|---------|---------|

| アドレス  | 15   | 50    | × 44.7pf | × 10mhz | × 10.9v | =0.037W |

| MSO   | 1    | 0     | × 44.7pf | × 10mhz | × 10.9v | =0.000W |

| WR    | 1    | -     | × 44.7pf | × 20mhz | × 10.9v | =0.010W |

| データ   | 32   | 50    | × 14.7pf | × 10mhz | × 10.9v | =0.026W |

| アドクルク | 1    | -     | × 4.7pf  | × 20mhz | × 10.9v | =0.001W |

$$pext=0.074W$$

## 絶対最大評価

表7よりも大きい応力は、デバイスに永久的な損傷を引き起こす可能性があります。これらはストレス評価のみです。これらまたはその他により大きな条件でのデバイスの機能的動作

この仕様の操作セクションで示されているものよりも暗示されています。長期間にわたって絶対最大定格条件にさらされると、デバイスの信頼性に影響を与える可能性があります。

表7。絶対最大評価

| パラメータ；パラメータ | ADSP-21060/ADSP-21060C<br>広告-21062<br>5V. | ADSP-21060L/ADSP-21060<br>LC ADSP-21062L<br>3.3V. |

|-------------|-------------------------------------------|---------------------------------------------------|

| 電源電圧(VDD)   | -0.3V~+7.0V                               | -0.3V~+4.6V                                       |

| 入力電圧        | -0.5V~VDD+0.5V                            | -0.5V~VDD+0.5V                                    |

| 出力電圧スイング    | -0.5V~VDD+0.5V                            | -0.5V~VDD+0.5V                                    |

| 負荷容量        | 200 pF                                    | 200 pF                                            |

| 保存温度範囲      | -65°C~+150°C                              | -65°C~+150°C                                      |

| 鉛温度(5秒)     | 280°C                                     | 280°C                                             |

| バイアス下接合温度   | 130°C                                     | 130°C                                             |

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

## ESDの注意

ESD(静電放電)感受性デバイス。充電されたデバイスおよび回路基板は、検出せずに放電できます。この製品は特許取得済みまたは独自の保護回路を備えていますが、高エネルギーESDを受けるデバイスに損傷が発生する可能性があります。したがって、パフォーマンスの低下や機能の損失を避けるために、適切なESD予防措置を講じる必要があります。

## パッケージマーキング情報

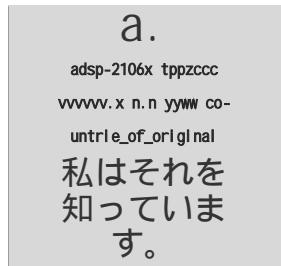

図8と表8は、ADSP-2106xプロセッサのパッケージマーク内に含まれる詳細に関する情報を提供します（実際のマーキング形式は異なる場合があります）。製品の可用性の完全なリストについては、62ページの注文ガイドを参照してください。

図8. 典型的なパッケージブランド

表8. パッケージブランド情報

| ブランドキー   | フィールド記述            |

|----------|--------------------|

| tpp      | 温度範囲パッケージタイプ       |

| Z ; Z    | リード(Pb)フリーオプション注   |

| cccの     | 文ガイドアセンブリロットコードを参照 |

| vvvvvv.x | シリコンリビジョン日付コードを参照  |

| n.n      |                    |

| yyww     |                    |

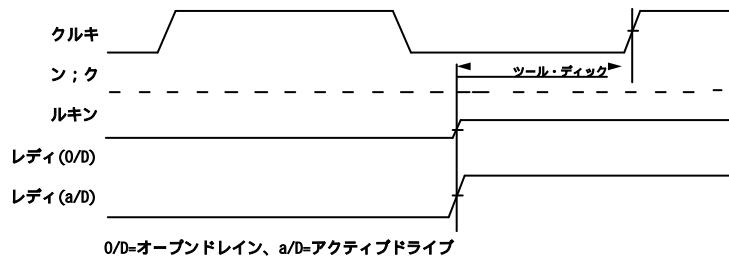

## タイミング仕様

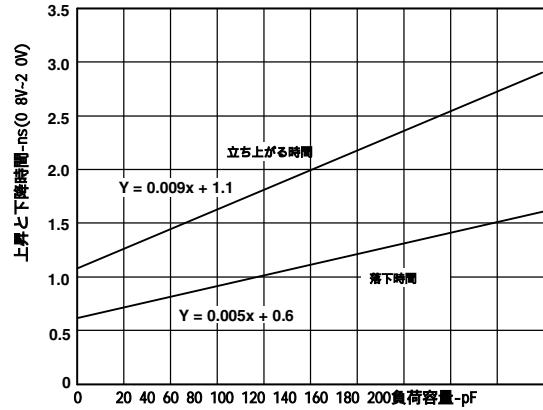

ADSP-2106xプロセッサは、最大プロセスまたは33mhz (-133)および40mhz(-160)の速度で利用できます。タイミング仕様は、40 MHz tCK=25 nsのCLKIN周波数に基づいています。DTデレーティング係数は、tCK仕様の最小から最大範囲内のタイミング仕様の計算を可能にします（表9を参照）。DTは、減少したCLKIN期間と25 nsのCLKIN期間との差分です。

$$DT=tck-25 \text{ ns}$$

与えられた正確なタイミング情報を使用します。他のパラメータの加算または減算からパラメータを導出しようとしないでください。加算または減算は個々のデバイスにとって有意義な結果をもたらしますが、このデータシートで与えられた値は統計的な変動と最悪のケースを反映しています。その結果、パラメータを有意義に追加してより長い時間を導出することはできません。電圧基準レベルについては、試験条件下のページ48の図28を参照してください。

タイミング要件は、読み出し動作のために入力されたデータなど、プロセッサの外部のcirによって制御される信号に適用されます。タイミング要件は、プロセッサが他のデバイスで正しく動作することを保証します。（0/D）=オーブンドレイン、（a/D）=アクティブドライブ。

スイッチング特性は、プロセッサが信号をどのように変更するかを指定します。このタイミングを制御することはできません。プロセッサ外部の回路は、これらの信号特性と互換性があるように設計されている必要があります。スイッチング特性は、特定の状況でプロセッサが何をするかを示します。また、スイッチング特性を使用して、プロセッサに接続されているデバイス（メモリなど）のタイミング要件を満たすこともできます。

# ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC

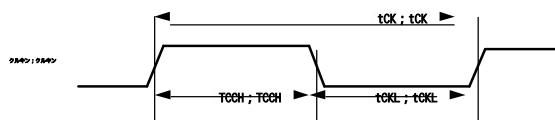

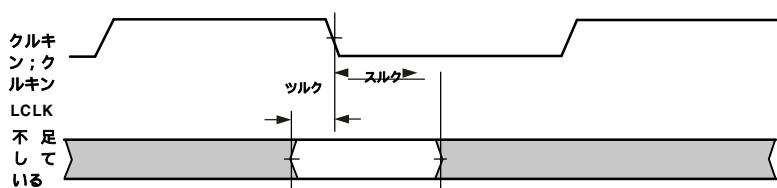

## クロック入力

表9。クロック入力

| パラメータ；パラメータ                  | 広告-21060<br>広告-21062<br>40 MHz、5v | 広告-21060<br>広告-21062<br>33 MHz、5v | 広告-21060L<br>広告-21062L<br>40 MHz、3.3v | 広告-21060L<br>広告-21062L<br>33 MHz、3.3v | ユニット |    |

|------------------------------|-----------------------------------|-----------------------------------|---------------------------------------|---------------------------------------|------|----|